In the main EDI window, click "Floorplan" → "Specify Floorplan ..."in the main menu.

In the "Specify Floorplan" window, you will see the core utilization set to 0.7.

Use the following settings for your design and click "OK". (Do not change other seetings).

Core utilization: 0.6

Core to Left: 5.0

Core to Top: 5.0

Core to Right: 5.0

Core to Bottom: 5.0

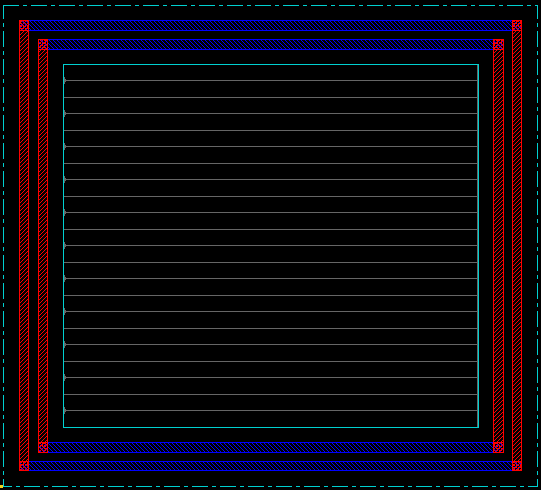

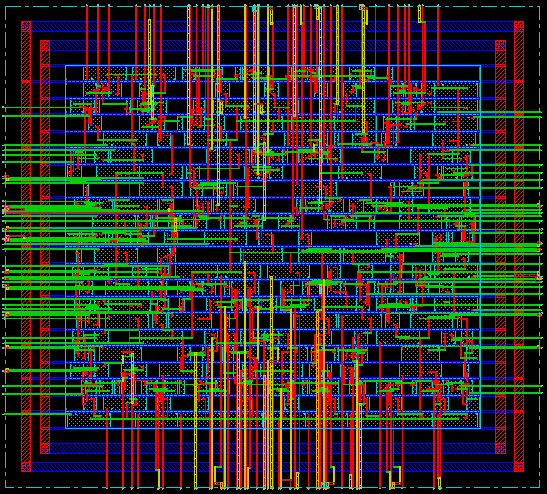

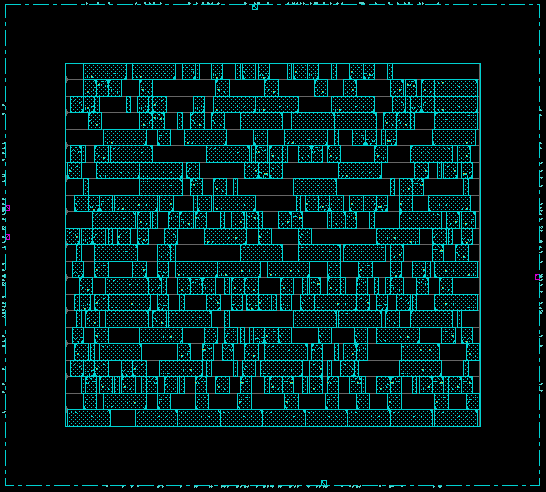

Now, you will see a modified floorplan as follows.

Save your design. Click "File" → "Save Design". Choose "Encounter" instead of "OA". In the file name, type VRCA64_01_FL.enc and click "OK". Note that postfix "01_FL" denotes the current design step.