#### EE 434 ASIC and Digital Systems

Prof. Dae Hyun Kim School of Electrical Engineering and Computer Science Washington State University

#### **Preliminaries**

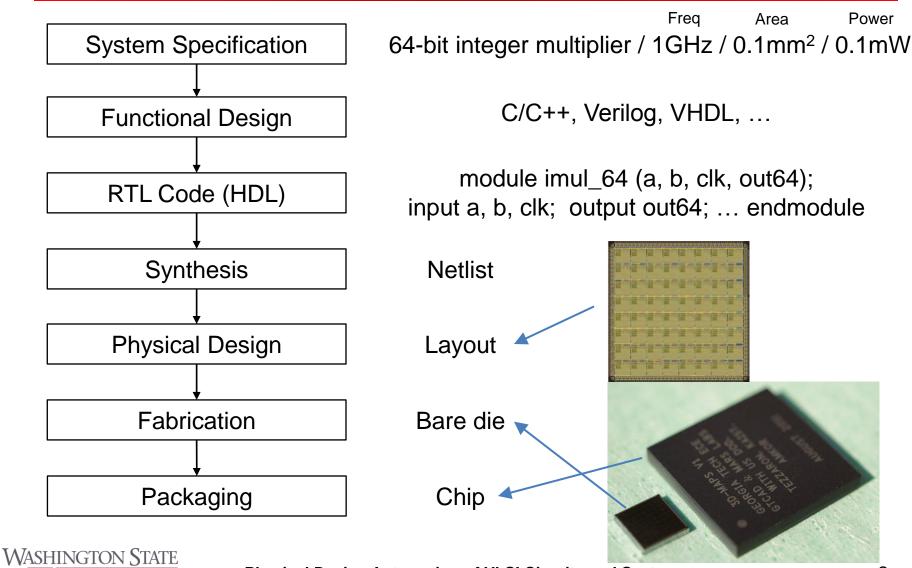

# **VLSI** Design

Physical Design Automation of VLSI Circuits and Systems

**JNIVERSITY**

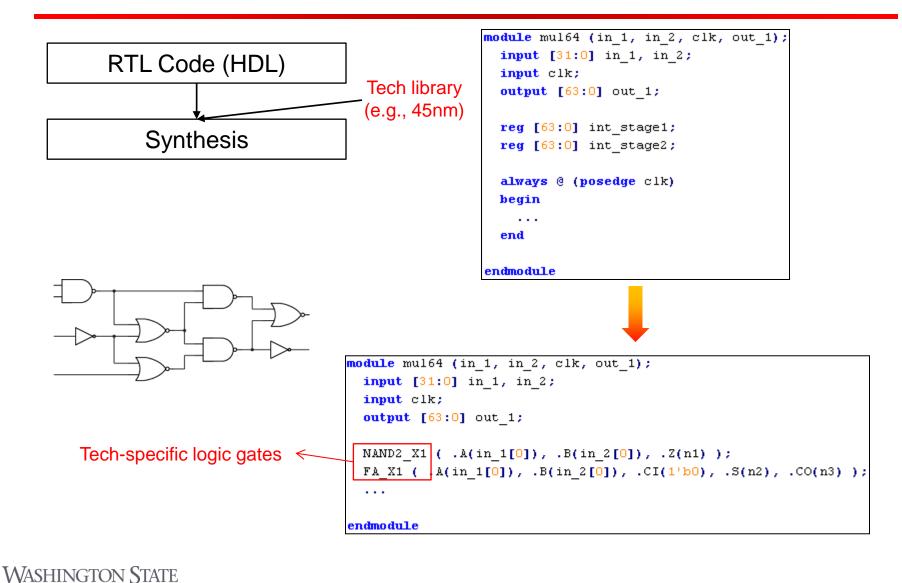

#### RTL Code (HDL)

```

module mul64 (in_1, in_2, clk, out_1);

input [31:0] in_1, in_2;

input clk;

output [63:0] out_1;

reg [63:0] int_stage1;

reg [63:0] int_stage2;

always @ (posedge clk)

begin

...

end

endmodule

```

**J** JNIVERSITY

**Physical Design Automation of VLSI Circuits and Systems**

[ JNIVERSITY

# **VLSI** Design

|                     | Full custom    | ASIC                |

|---------------------|----------------|---------------------|

| Design              | Manual         | Automatic           |

| TRs                 | Manually drawn | Standard-cell based |

| Placement & Routing | Custom         | Automatic           |

| Development time    | Several months | A few days ~ weeks  |

- Provides

- good performance

- low power

- small area

- ...

- Other design styles

FPGA

- PLA

- Standard cells

- A set of logic gates

- Have the same height.

- Width varies.

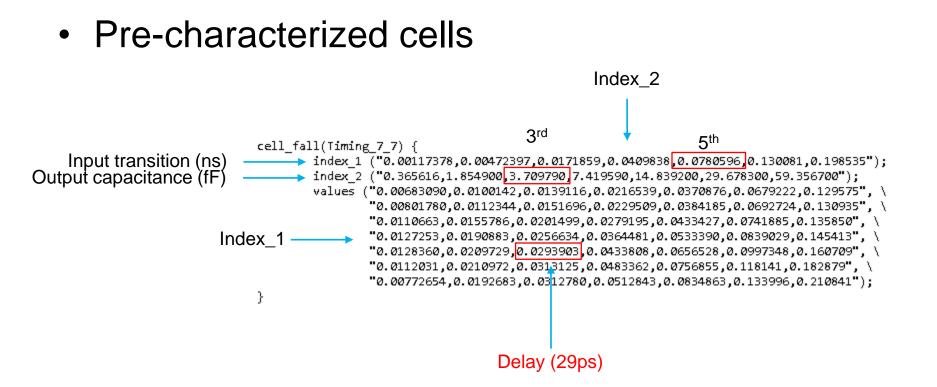

- Pre-characterized for timing and power analysis.

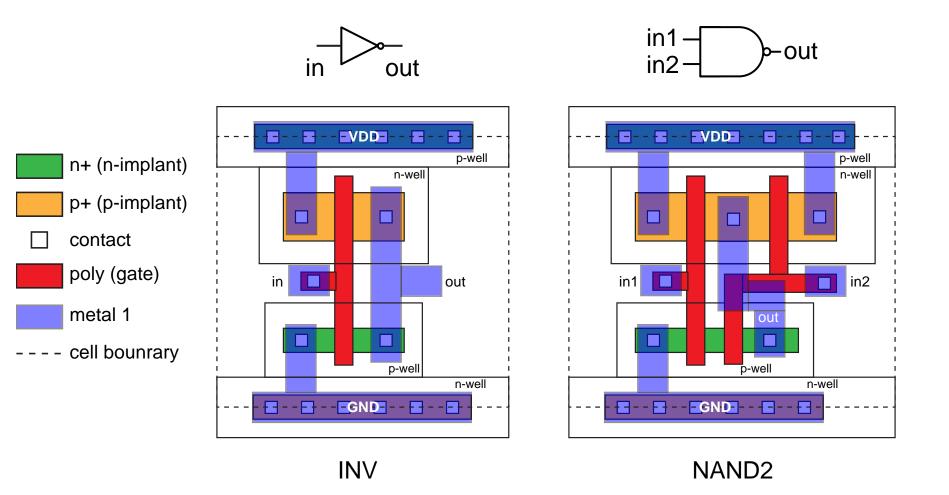

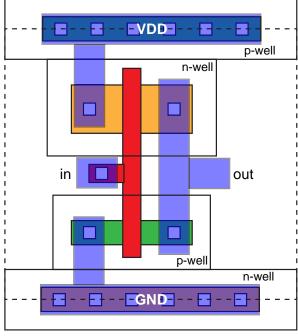

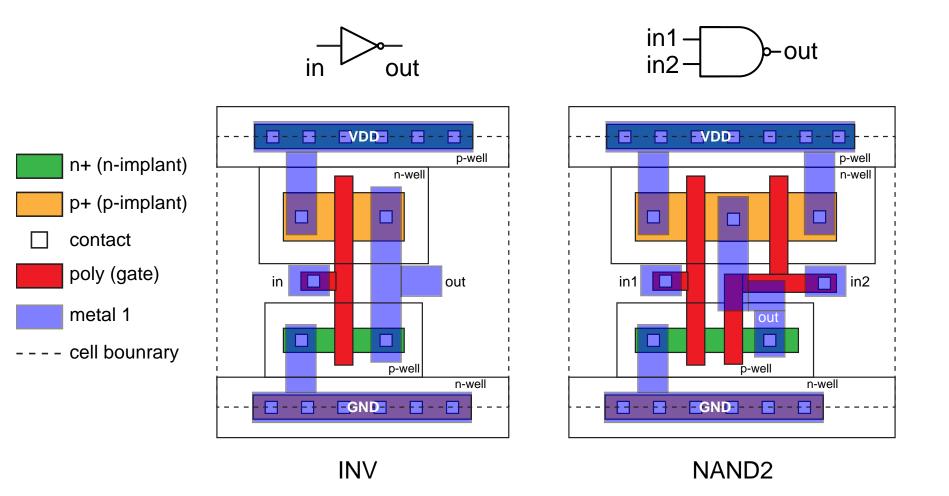

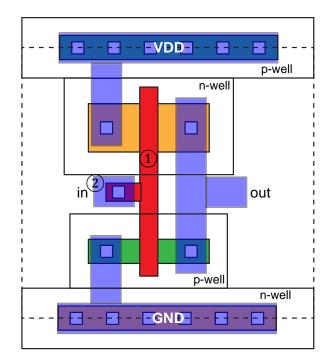

# **Standard Cells (Layout)**

WASHINGTON STATE UNIVERSITY

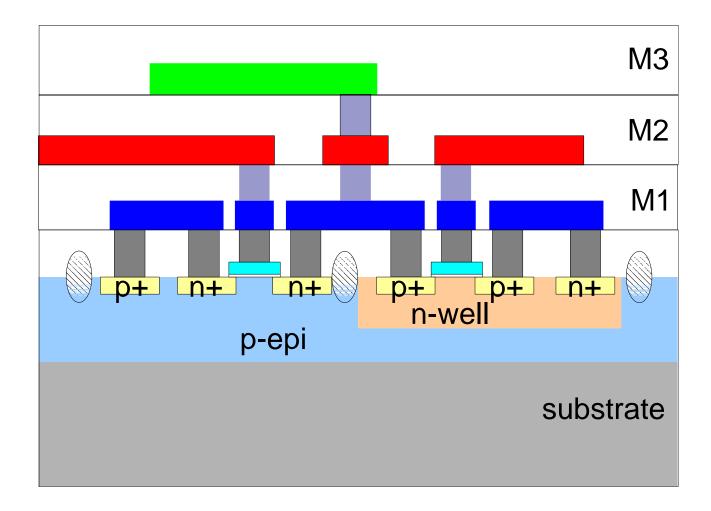

# **Standard Cells (Layout)**

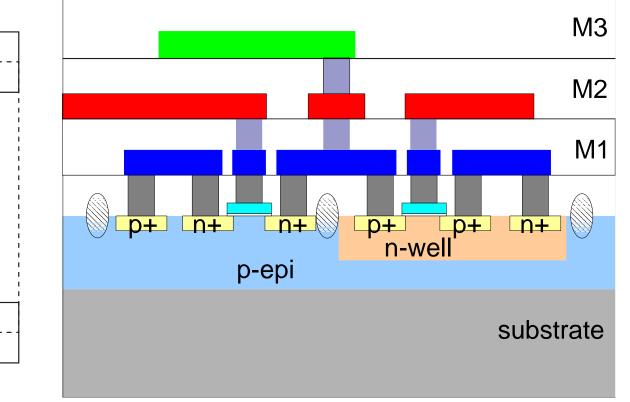

Top-down view

Side view

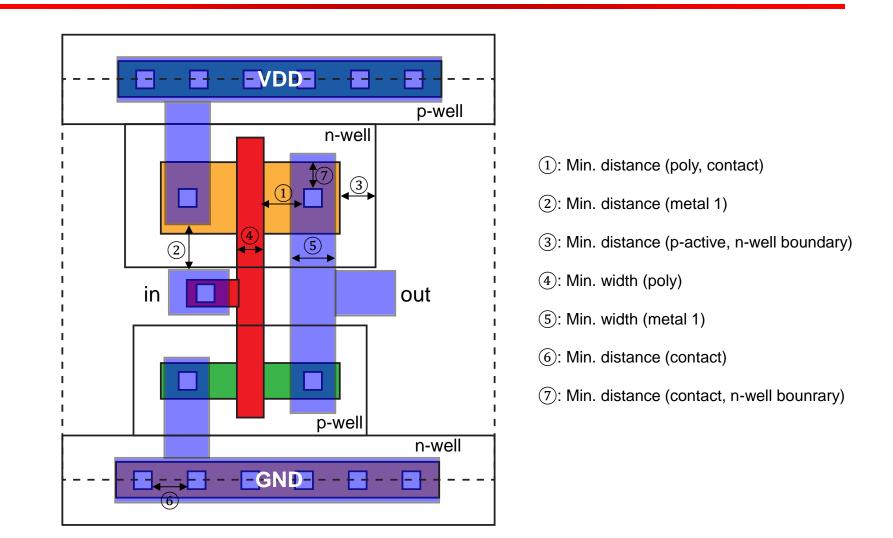

# **Design Rules**

# **Standard Cells (Layout)**

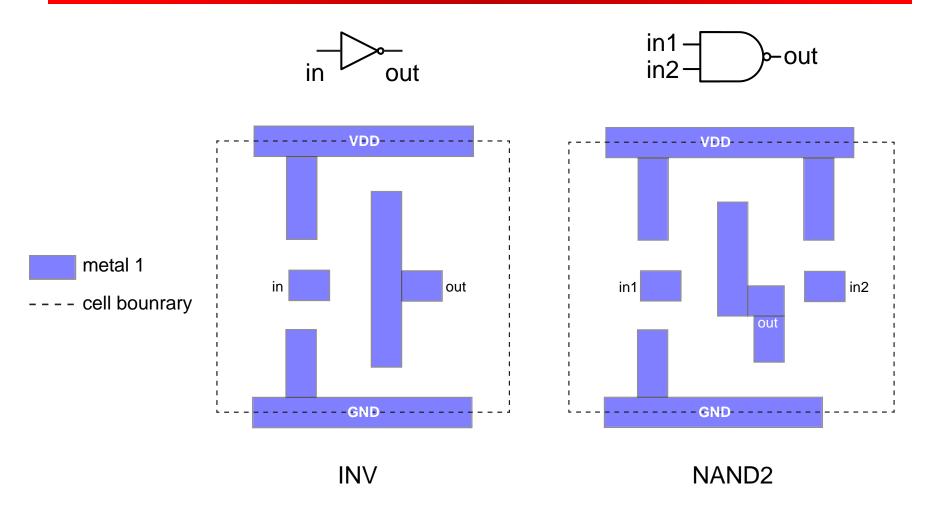

### **Standard Cells (Abstract)**

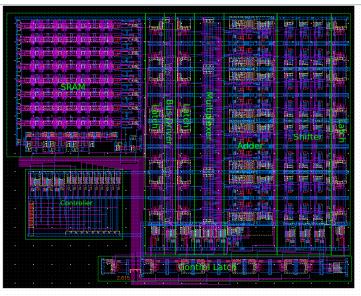

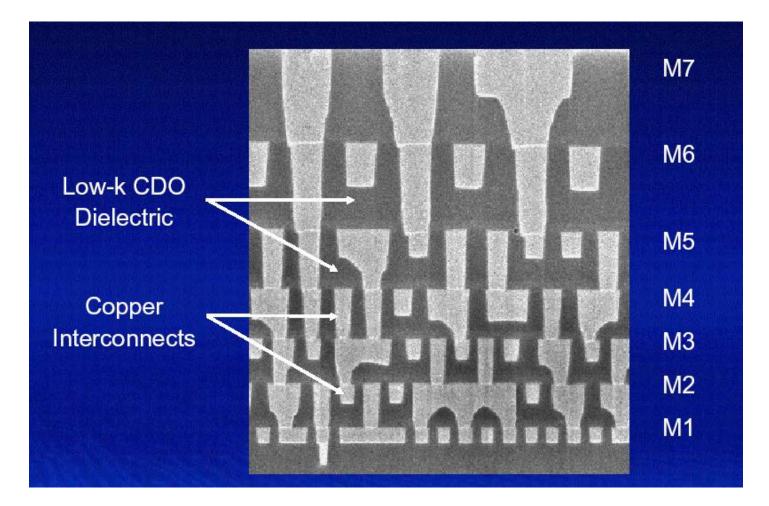

- Deal with

- Standard cells (pre-drawn and pre-characterized)

- Routing layers (M1, via12, M2, via23, ...)

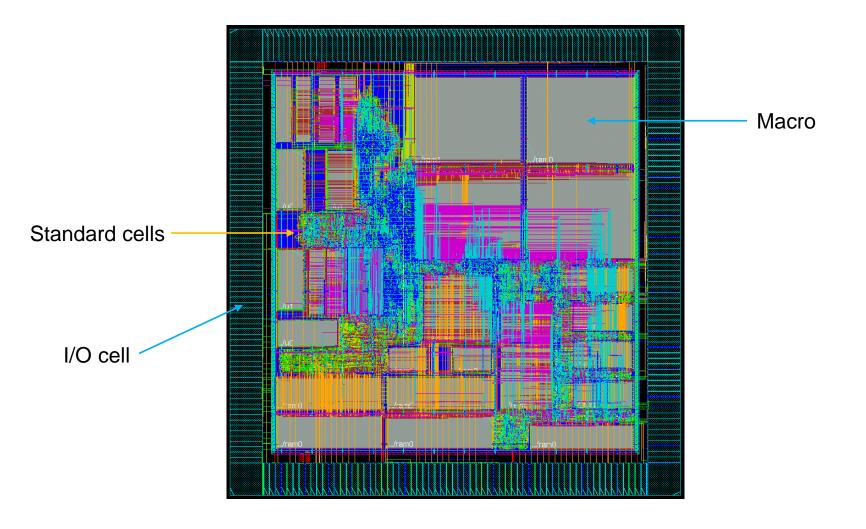

- Intellectual Property (IP) blocks

- Pre-created blocks

- Memory

- Arithmetic

- Cryptographic

- DSP

- Controller

- ...

# **Delay Calculation & Timing Analysis**

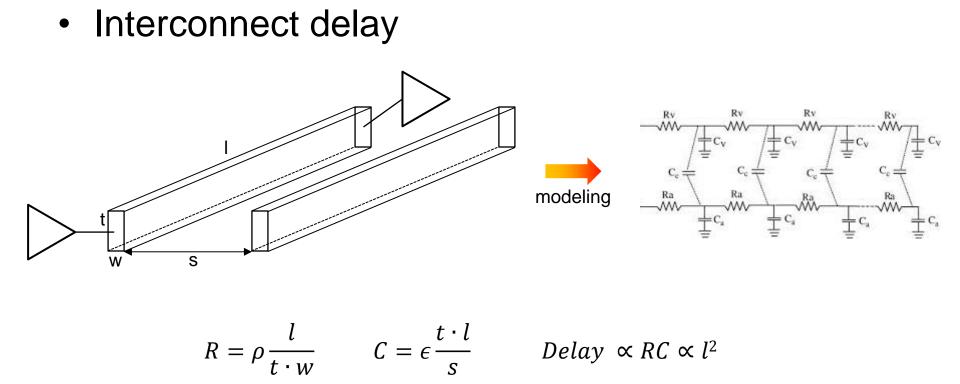

## **Delay Calculation**

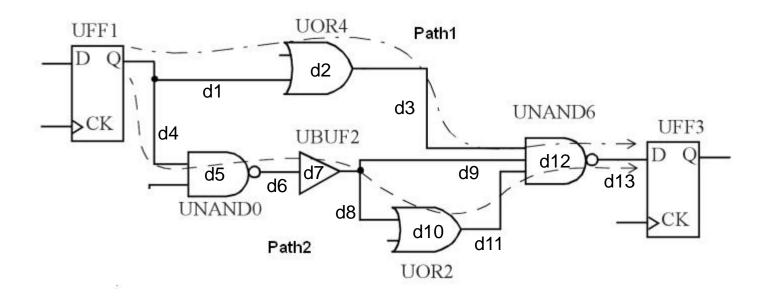

# **Timing Analysis**

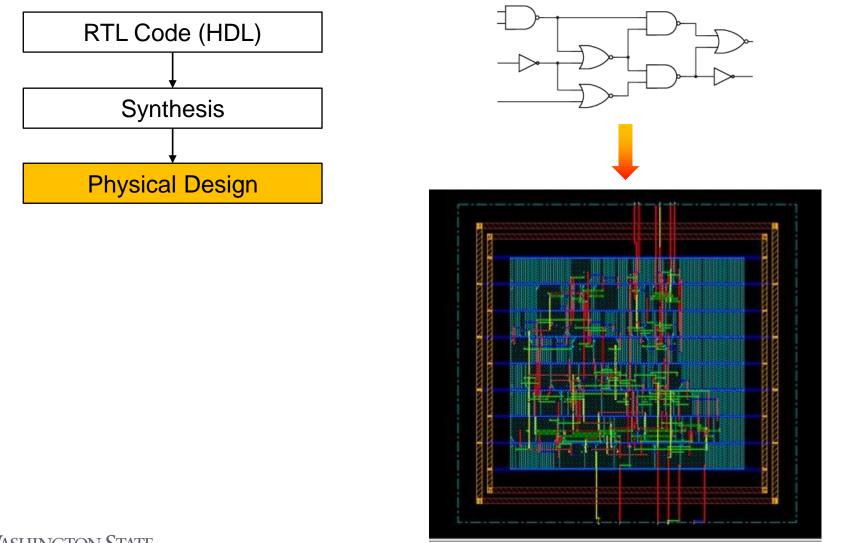

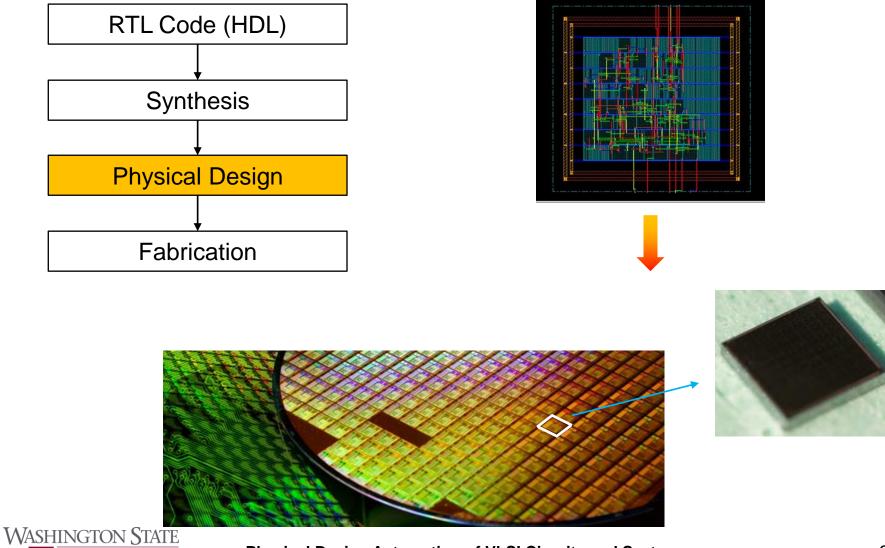

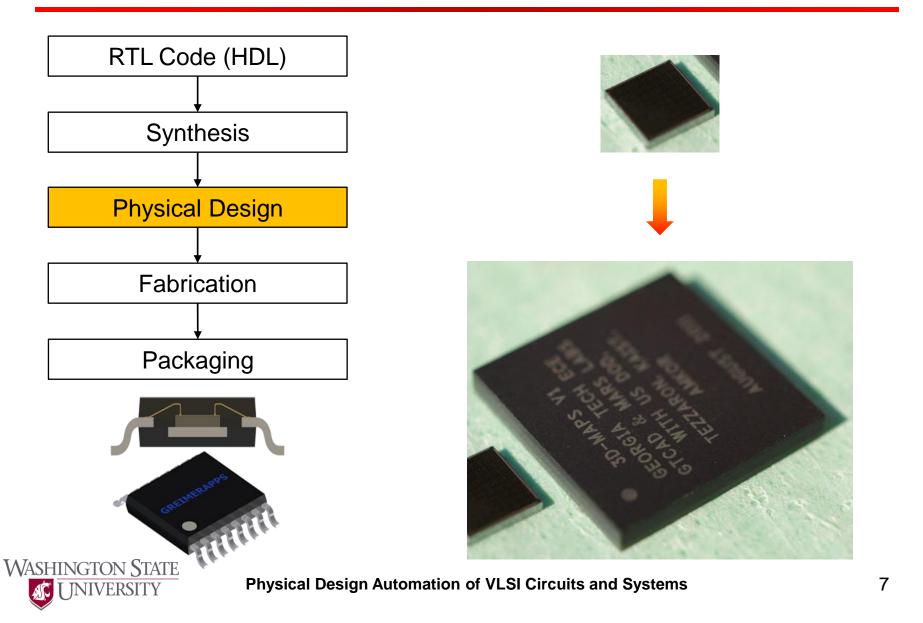

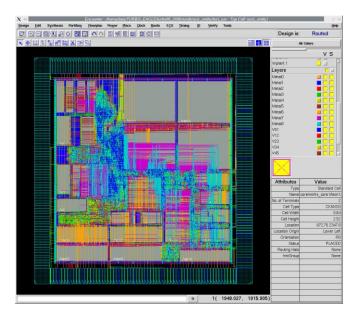

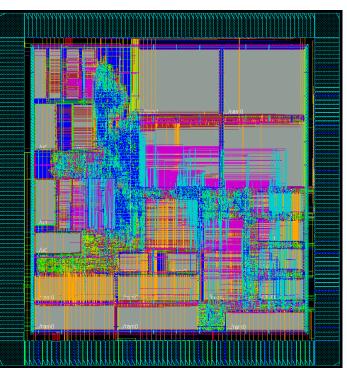

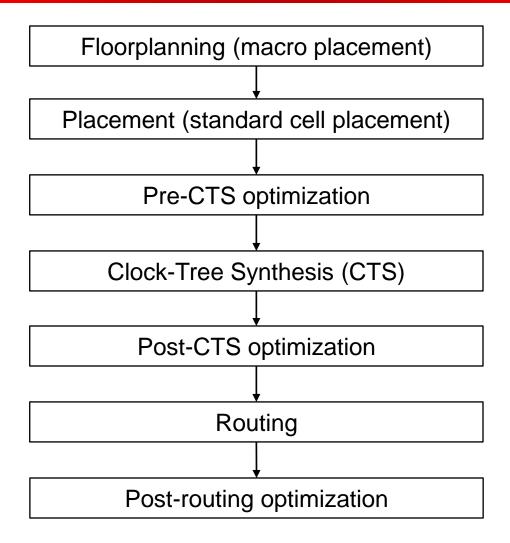

- What should we do?

- Find the locations of the macros.

- Find the locations of the standard cells.

- Route the macros and the standard cells.

- Power/ground

- Signal

- Clock

- Bus

- Extract parasitic RC.

- Analyze the final layout.

- Timing (clock frequency)

- Power consumption (dynamic / leakage)

- Area

- Power integrity

- Signal integrity

- Thermal

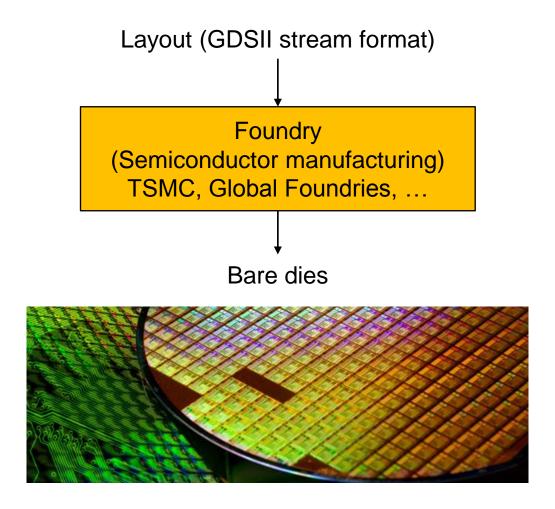

- Input

- Layout (GDSII stream format)

- A set of geometric objects

- Layer id 3, polygon { 50, 40, 70, 40, 70, 220, 50, 220, 50, 140, 20, 140, 20, 110, 50, 110, 50, 40 }

- (2): Layer id 7, rectangle { 10, 105, 40, 150 }

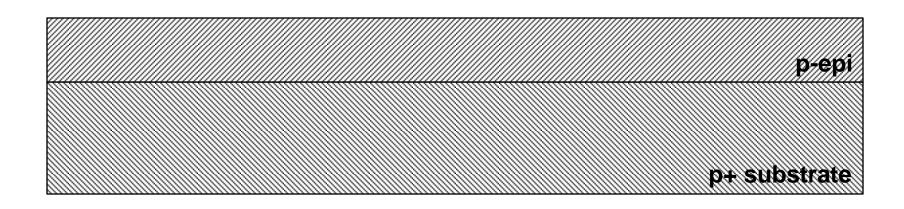

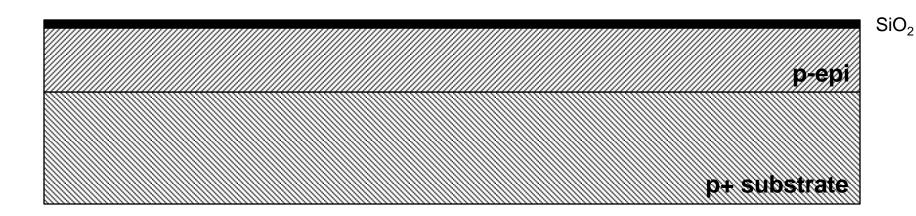

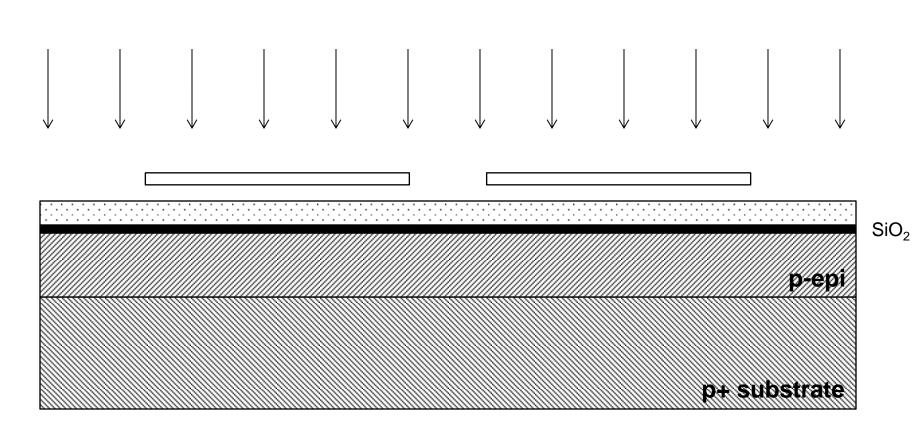

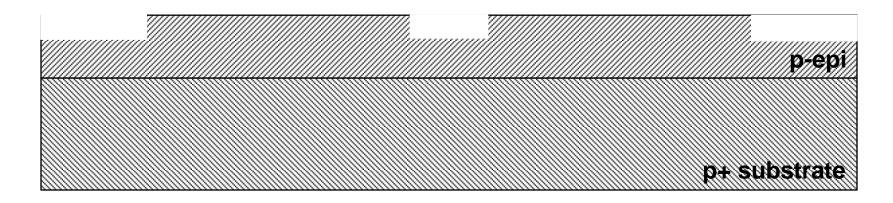

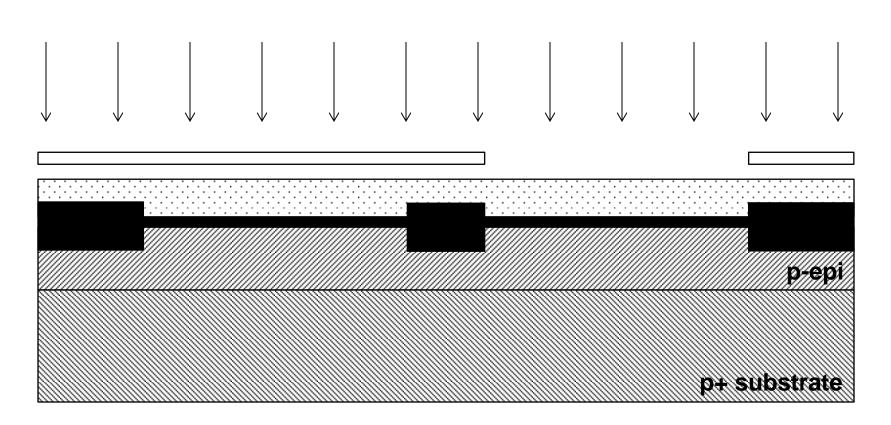

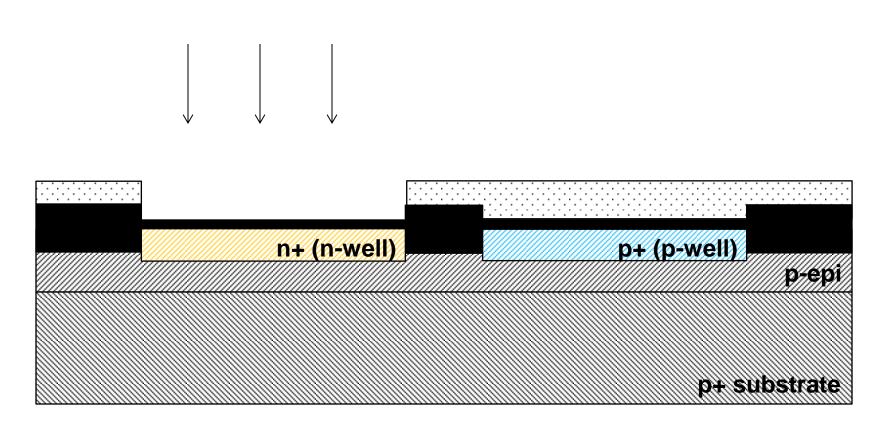

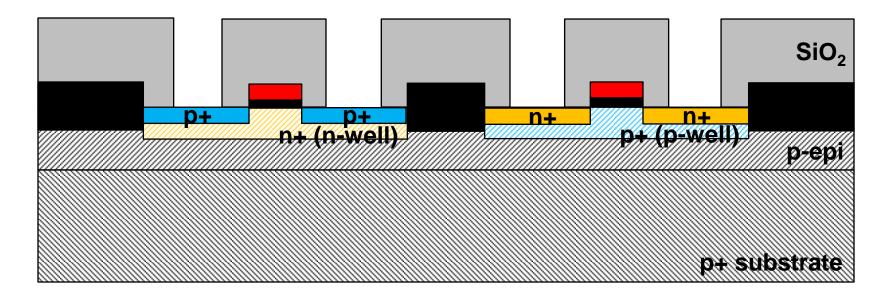

Gate-oxide deposition

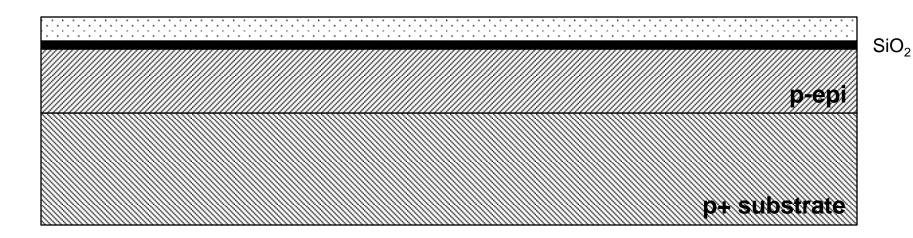

Photoresist

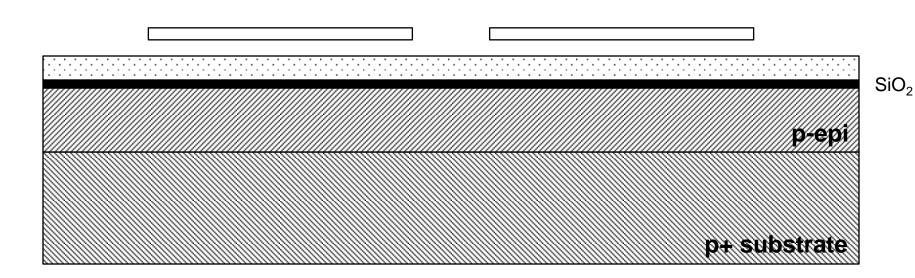

Mask

Expose (photolithography)

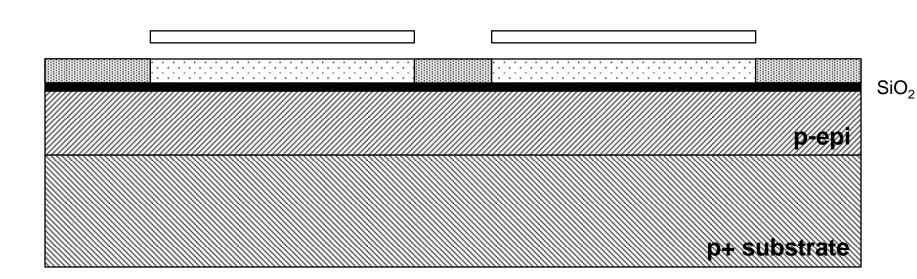

After photolithography

Remove mask

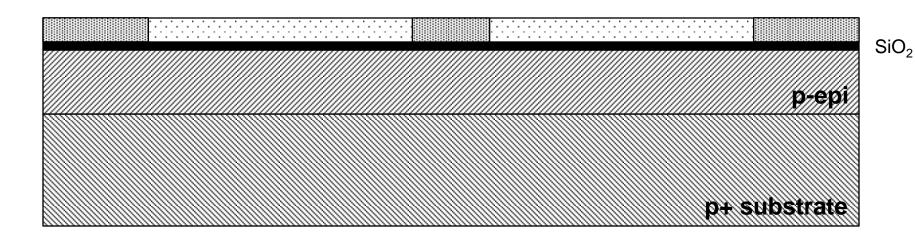

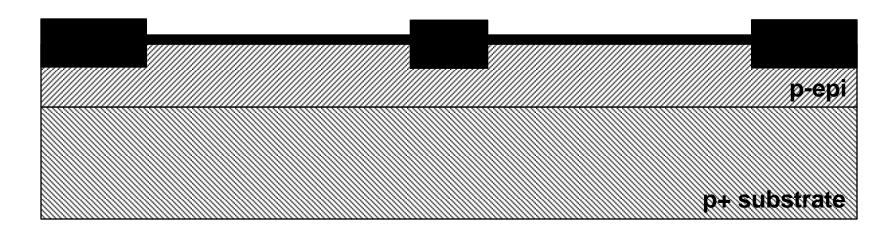

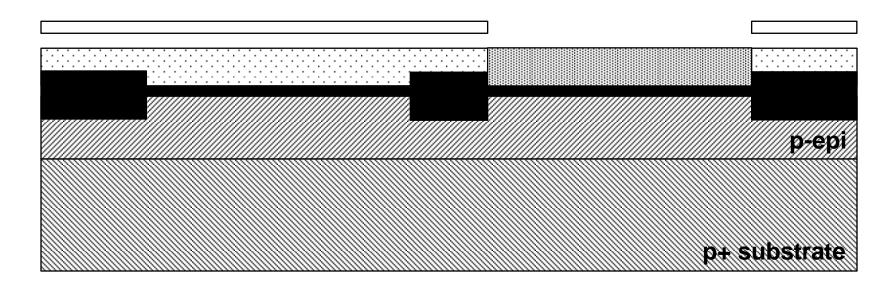

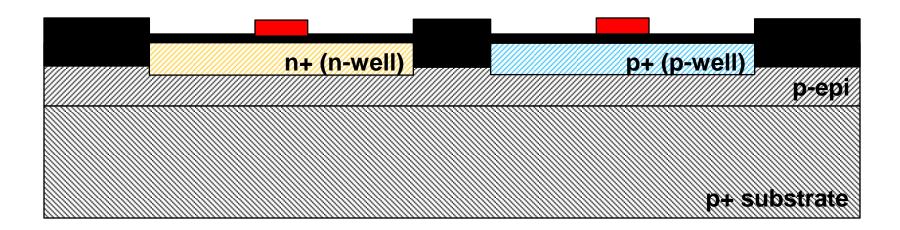

#### Etching

#### Etching

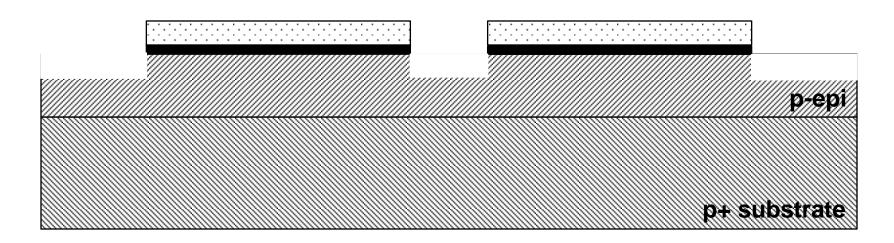

Oxide deposition

#### Photoresist

Mask

#### Photolithography

After photolithography

Etch

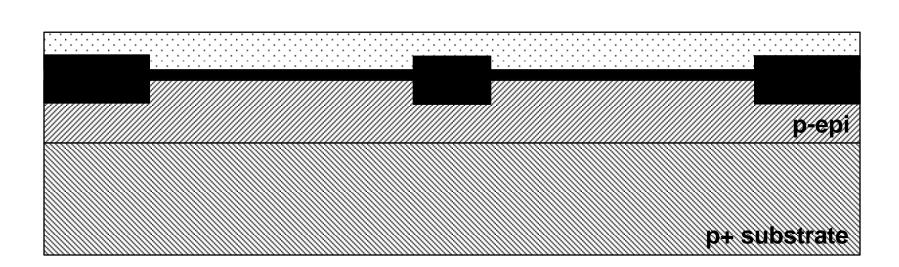

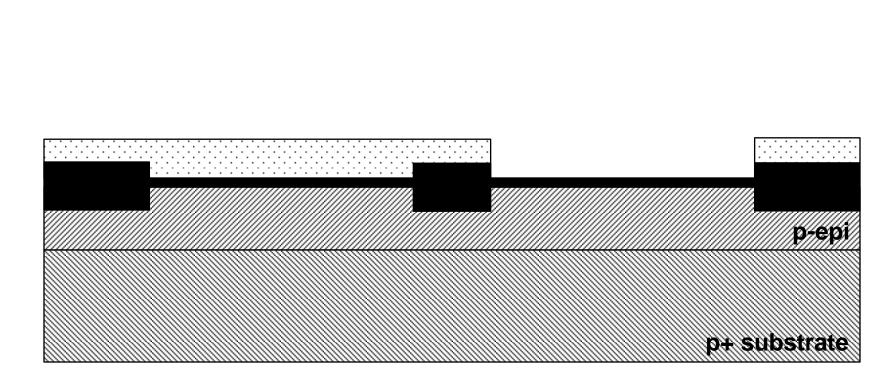

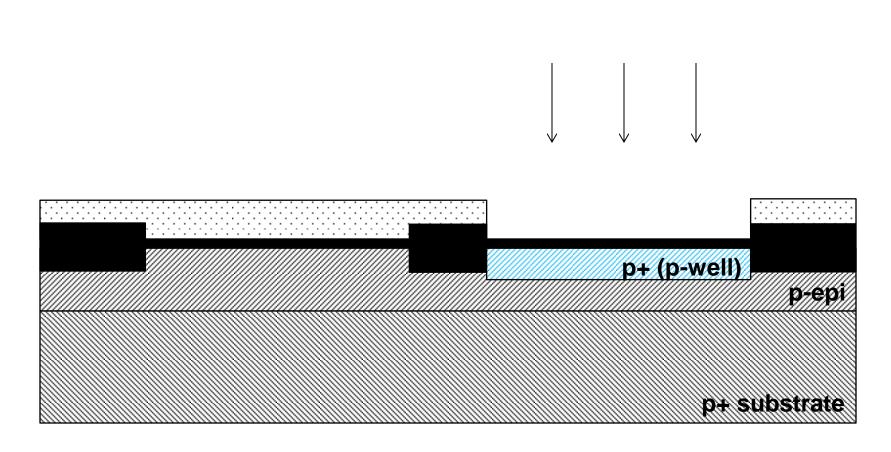

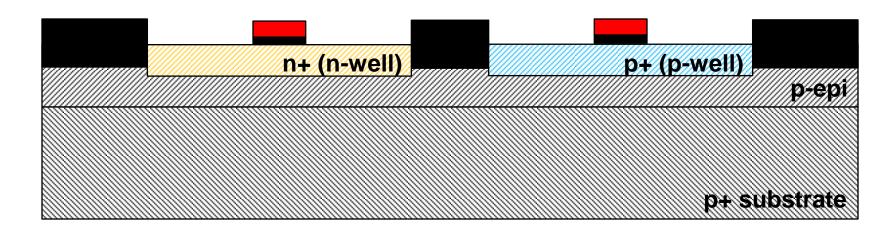

#### Doping

#### Doping

#### Poly

Etch

#### Doping

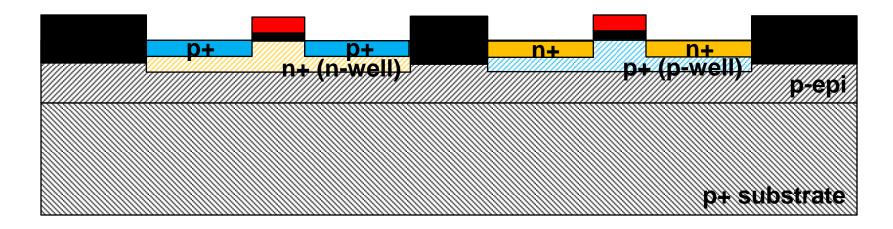

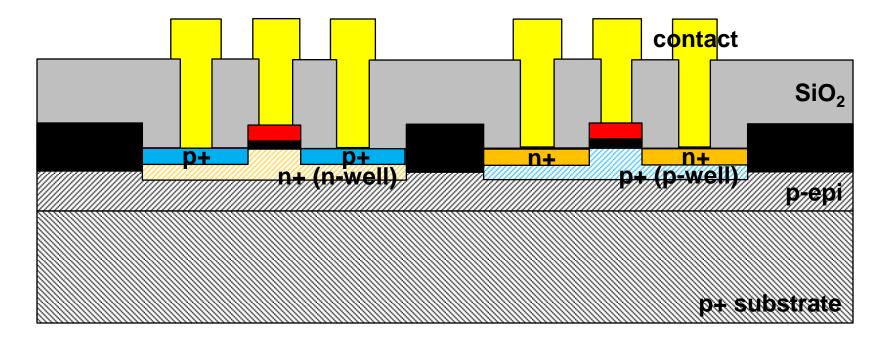

Oxide deposition

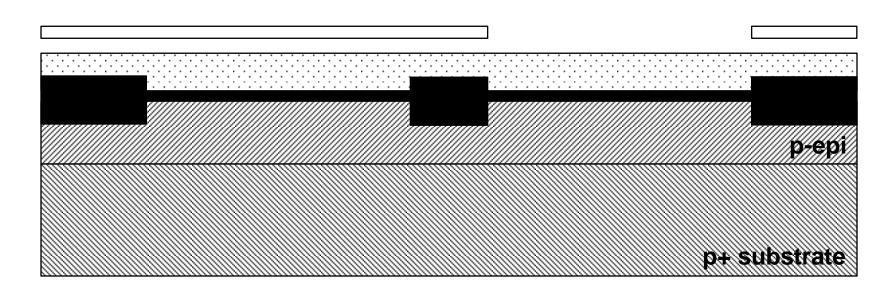

#### Contact

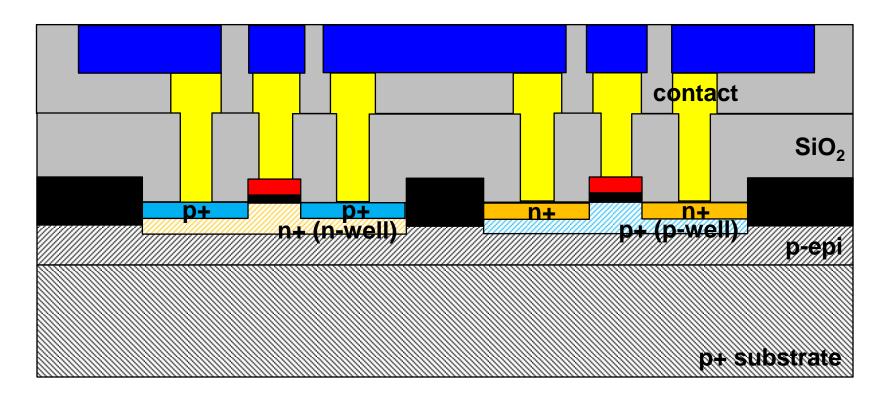

Metal 1

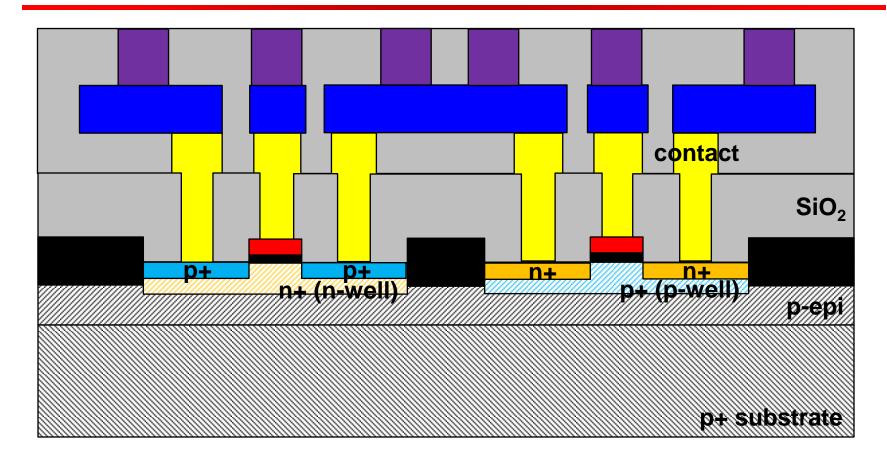

Via12

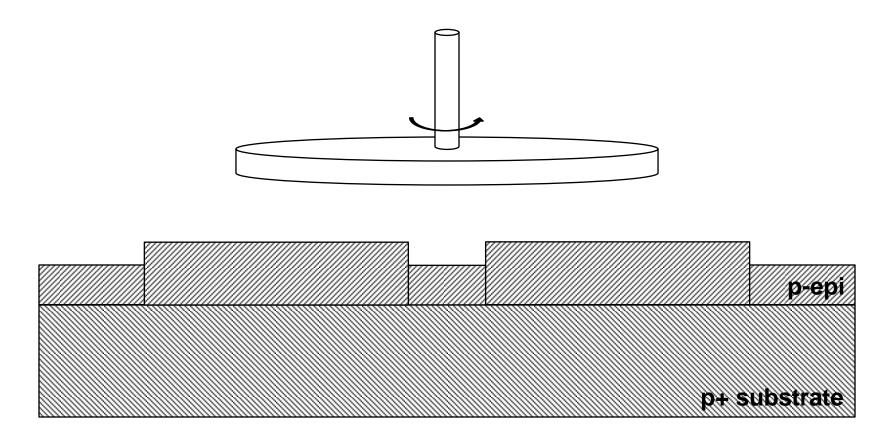

Chemical-mechanical-polishing (CMP)