## **Homework Assignment 4**

## (Due Mar. 4<sup>th</sup> at the beginning of the class)

- 0. Preparation for homework 4

- Download the following file into your working directory.

o wget http://www.eecs.wsu.edu/~ee434/Homework/hw04.tar.gz

- Unzip it.

•

o tar xvzf hw04.tar.gz

- Source synopsys.sh o source synopsys.sh

- 1. [Pseudo-nMOS, 20 points]

- Design a pseudo-nMOS inverter for the following design spec:

- $\circ$  Simulate the inverter with the following load cap and input signal

- Load cap: 10fF

- The fall & rise transition time of the input signal: 10ps

- $\circ$  Spec

- Rise time < 100ps

- Fall time < 100ps

- $V_{OL} < 100 mV$

- $V_{OH} > 900 mV$

- $NM_L > 150mV$

- $NM_H > 300mV$

- [Submit]

- $\circ$  The size of the NMOS and PMOS transistors

- o Rise time, fall time

- $\circ$  V<sub>IH</sub>, V<sub>IL</sub>, V<sub>OH</sub>, V<sub>OL</sub>, NM<sub>L</sub>, NM<sub>H</sub>

- o Average power for falling and rising transitions

- 2. [Dynamic CMOS, 20 points]

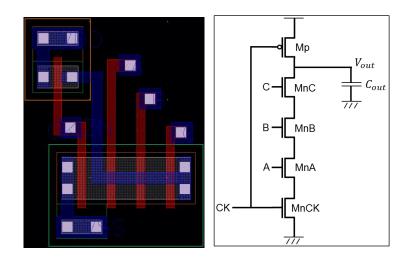

- We design a three-input NAND gate using the dynamic CMOS design style.

- Open myNAND3\_pex.cdl and see the netlist of the NAND gate. I drew a layout for the NAND gate and extracted parasitic RC. myNAND3\_pex.cdl includes all the parasitic RC.

- Open myNAND3\_simul.sp and see the netlist. It is used to simulate the NAND gate.

- The followings show the layout and schematic of the NAND gate.

- Add four signal waveforms (CK, A, B, C) to simulate charge sharing.

- o Load cap: 10fF

- $\circ CK: V_{DD} \to 0 \to V_{DD}$

- $\circ$  When CK is V<sub>DD</sub> (before it goes down to 0), set A, B, and C to V<sub>DD</sub> so that it can fully discharge the output capacitor and all the parasitic capacitors.

- $\circ$  Then, set A, B, and C to 0 before CK goes to 0.

- $\circ$  Then, CK goes to 0 and the gate will charge the output capacitor.

- $\circ$  Then, CK goes to  $V_{\text{DD}}$ .

- $\circ$  Then, set C to  $V_{DD}$  so that charge sharing can happen between the output capacitor and the parasitic capacitor between MnC and MnB.

- $\circ$  Perform the same simulation, but set both B and C to V<sub>DD</sub> so that charge sharing can happen among the output capacitor, the parasitic capacitors between MnC and MnB and between MnB and MnA.

- [Submit]

$\circ$  Vout when only C is set to V<sub>DD</sub> for C<sub>out</sub> =10fF, 9fF, ..., 1fF.

- [Submit]

- $\circ$  Vout when both C and B are set to V<sub>DD</sub> for C<sub>out</sub> =10fF, 9fF, ..., 1fF.

## 3. [Synthesis, 20 points]

- In this problem, we will synthesize a netlist for a few gates.

- Make sure you have the following files in your working directory.

- NangateOpenCellLibrary\_typical\_ecsm.db

nand8.v

- Source synopsys.sh.

- Run Design Compiler (DC).

- o design\_vision \_no\_gui

- In DC, run the following commands.

- o set link\_library {NangateOpenCellLibrary\_typical\_ecsm.db}

o set target\_library {NangateOpenCellLibrary\_typical\_ecsm.db}

o read\_file -format verilog {nand8.v}

o compile -exact\_map

o write -format verilog -output nand8\_mapped.v

o exit

- The two "set" statements set up target libraries.

- "read\_file" reads HDL source codes.

- "compile" compiles (synthesizes) the source codes.

- "write" writes the synthesized code into the file specified after "-output".

- Open "nand8.v" and see the function of the module.

- Open "nand8\_mapped.v" and see the function of the module. Are they equal?

- [Submit] Draw a schematic for the netlist of "nand8\_mapped.v".

- Implement a 20-input nand gate by modifying "nand8.v" and synthesize it.

- [Submit] Draw a schematic for the netlist of the synthesized 20-input nand gate.

- Implement a full adder and synthesize it.

- o Primary inputs: A, B, CI

- o Primary outputs: S, CO

- Use ^, &&, and || for XOR, logical AND, and logical OR operations in Verilog.

- Use parentheses to prioritize the operations.

- $\circ$  Use two assignments, one for S and the other for CO.

- [Submit] Draw a schematic for the netlist of the synthesized full adder.