EE 466/586 VLSI Design

Partha Pande School of EECS Washington State University pande@eecs.wsu.edu Lecture 16 Sequential Logic

# Sequential Logic

- 2 storage mechanisms

- positive feedback

- charge-based

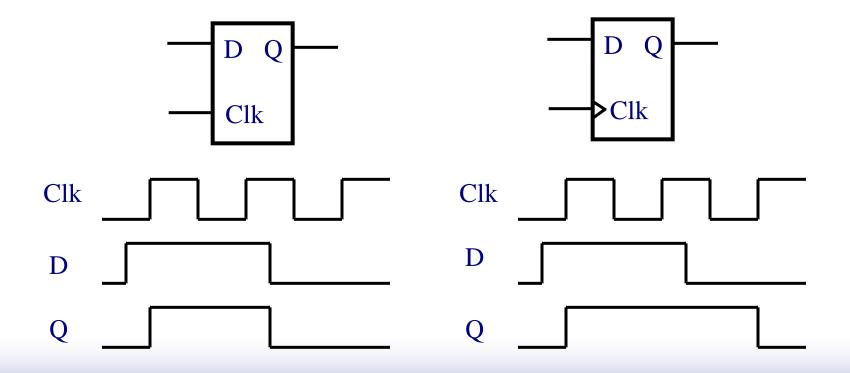

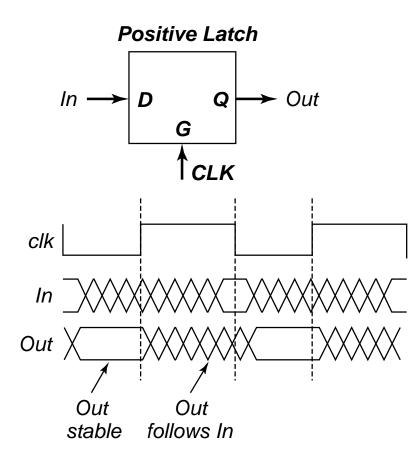

A latch is level sensitive

A register is edge-triggered

# Latch versus Register

Latch Stores data depending on the level of the clock Register stores data

when clock rises

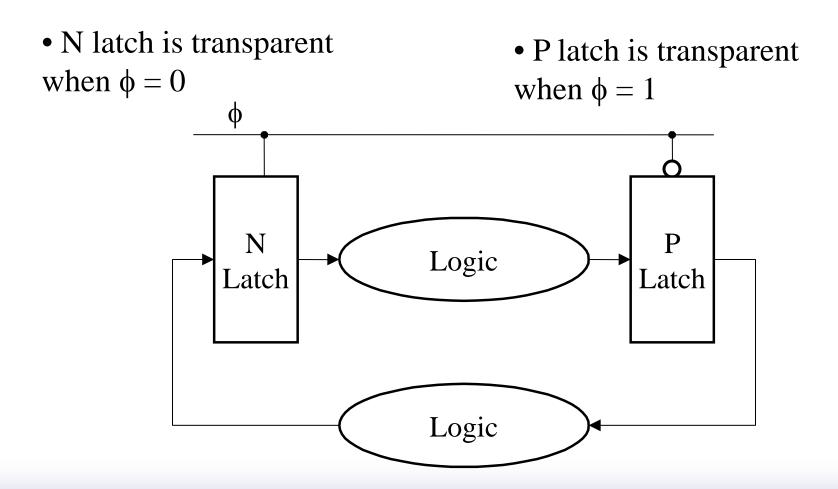

## Latch-Based Design

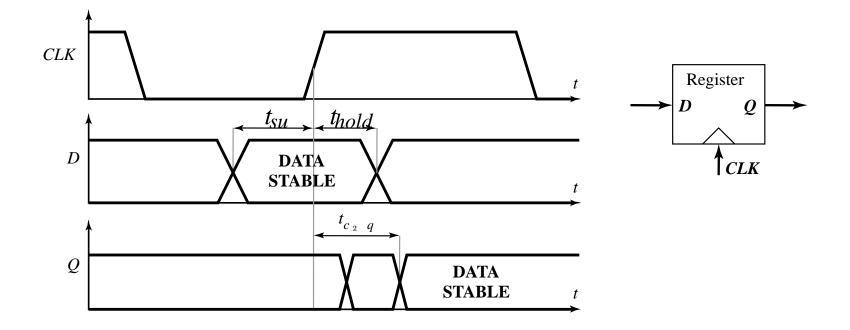

## **Timing Definitions**

# **Timing Definitions**

### □ T<sub>su</sub> (Setup time)

- Incoming data must be stable before the clock arrives

- □ T<sub>hold</sub> (Hold time)

- The length of time the data remains stable after the clock arrives for proper operation

- If the data is stable before the setup time and continues to be stable after the hold time, the register will properly capture the data

- □ T<sub>clk-Q</sub> (clk to Q delay)

- This is the delay from the time the clock arrives to the point at which the Q output stabilizes

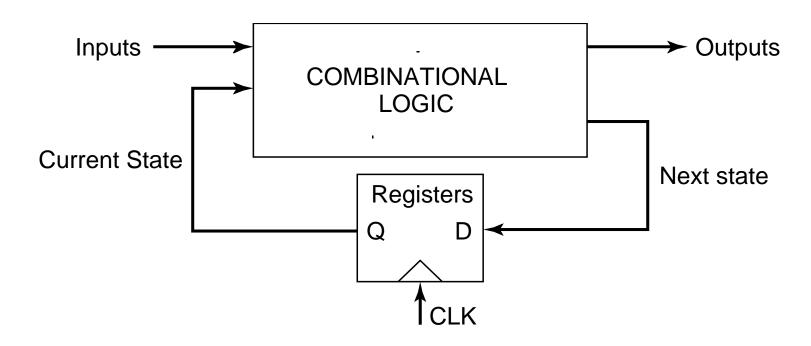

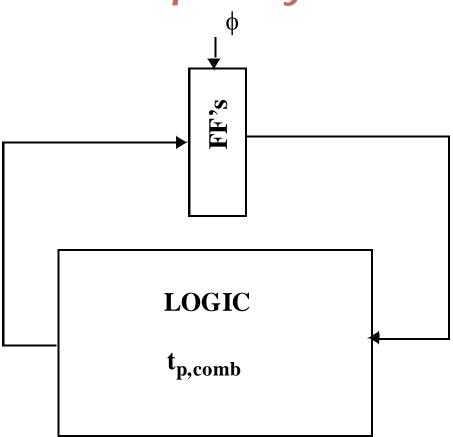

## Maximum Clock Frequency

$$t_{clk-Q} + t_{p,comb} + t_{setup} = T$$

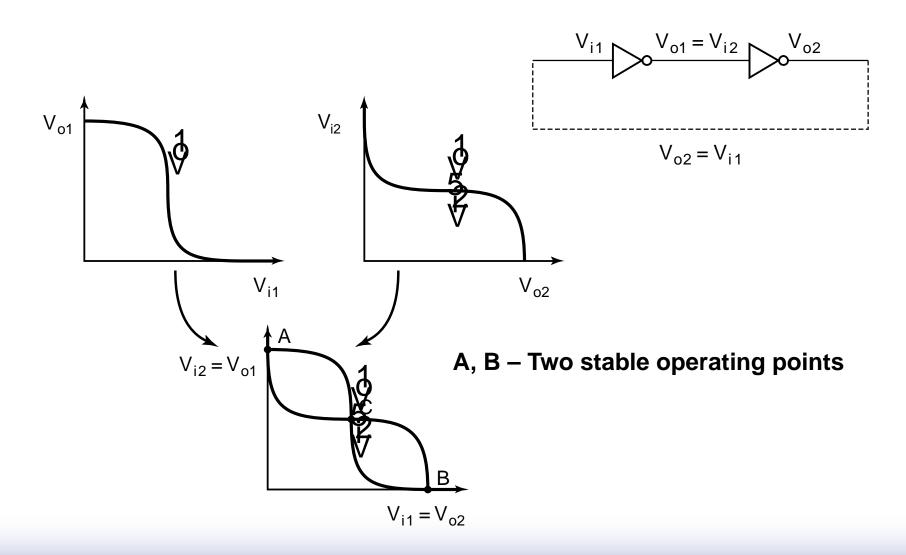

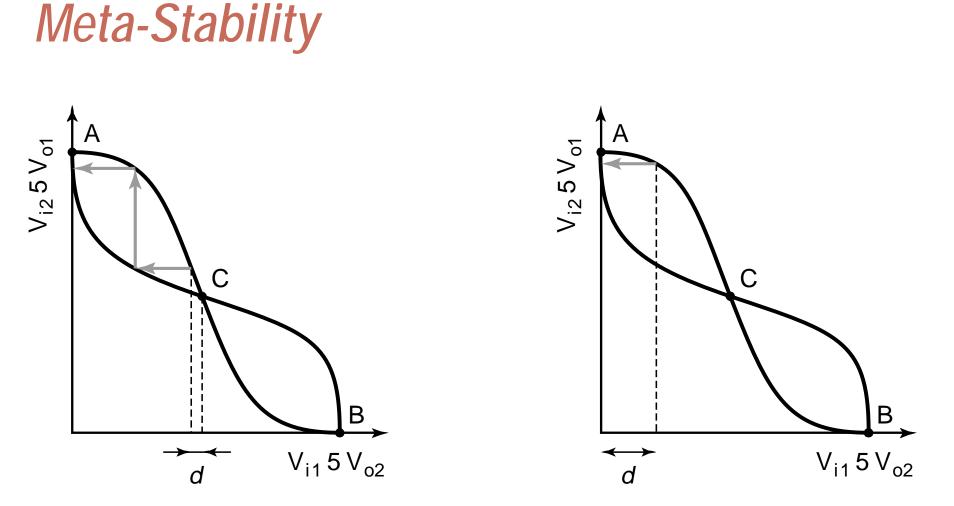

### Positive Feedback: Bi-Stability

Gain should be larger than 1 in the transition region

**Cross-Coupled Pairs**

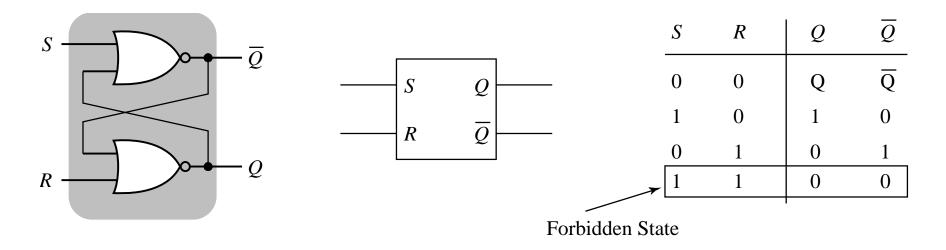

#### NOR-based set-reset

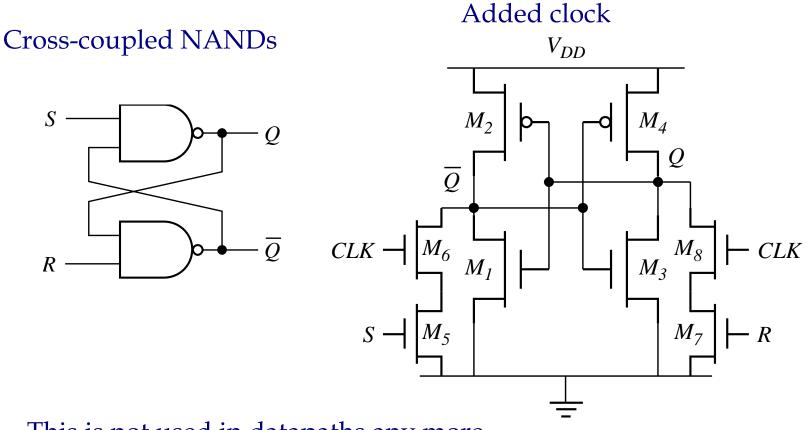

### **Cross-Coupled NAND**

This is not used in datapaths any more, but is a basic building memory cell

**Design of D-Latch**

□ Follow board notes

### Storage Mechanisms

### Static

Dynamic (charge-based)

Need a feedback loop to hold the data

## Making a Dynamic Latch Pseudo-Static

# Writing into a Static Latch

Use the clock as a decoupling signal, that distinguishes between the transparent and opaque states

Converting into a MUX

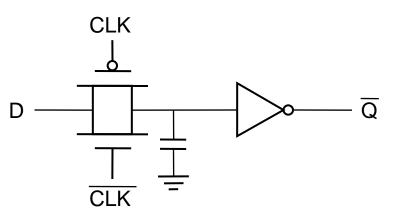

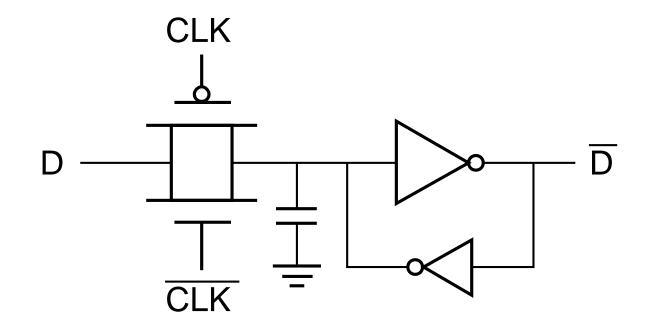

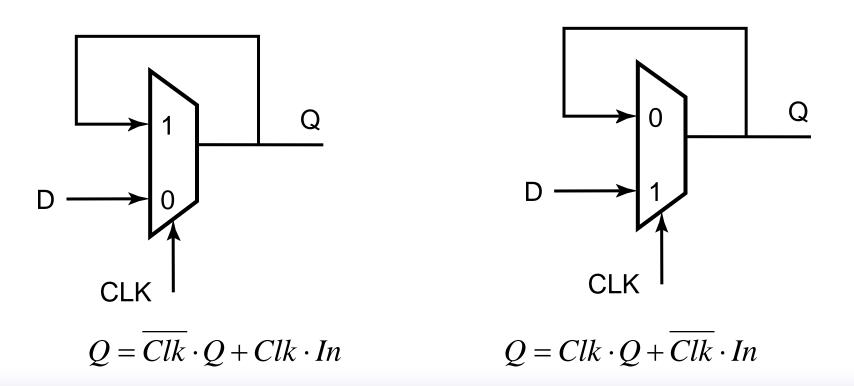

### Mux-Based Latches

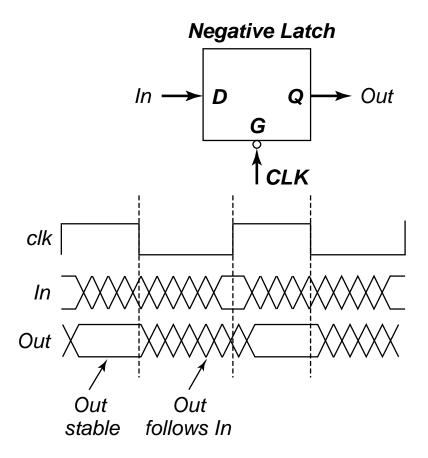

Negative latch (transparent when CLK= 0)

Positive latch (transparent when CLK= 1)

### Mux-Based Latch

### Mux-Based Latch

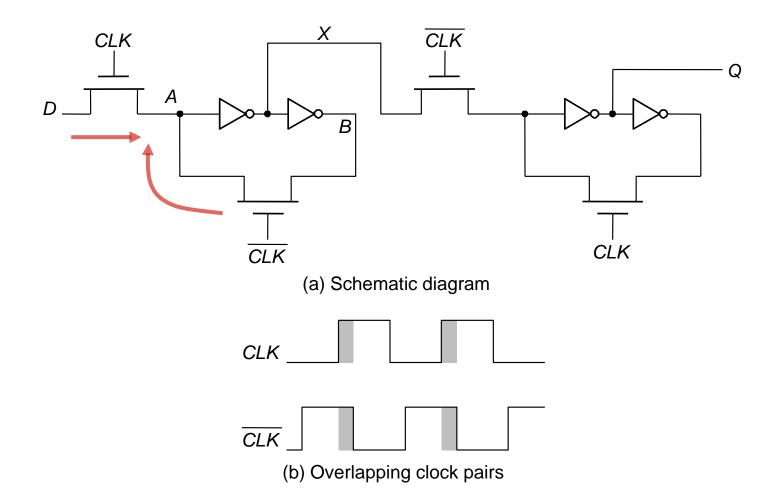

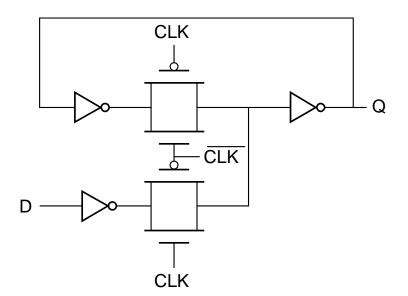

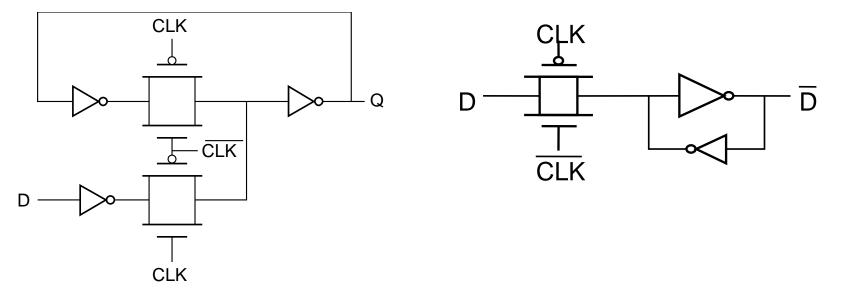

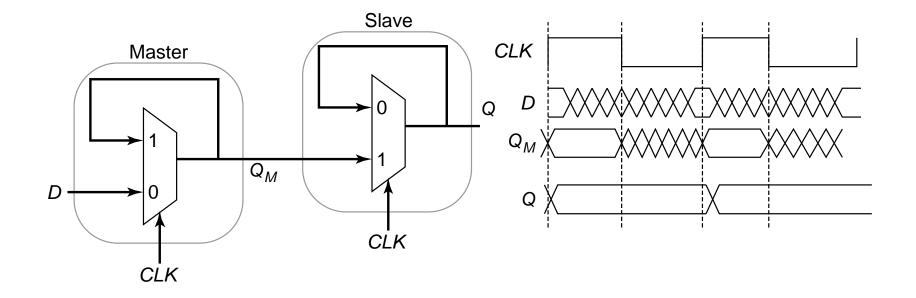

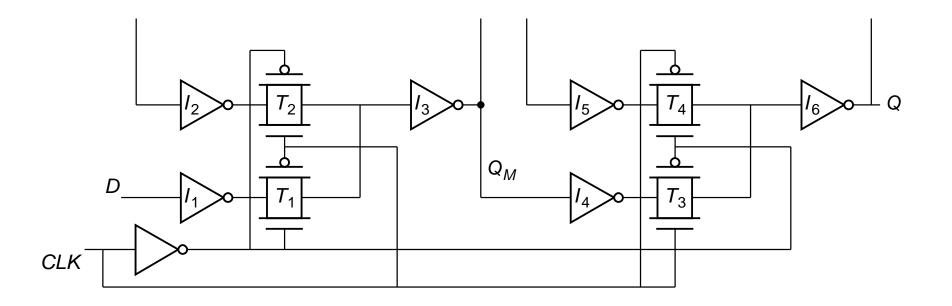

# Master-Slave (Edge-Triggered) Register

Two opposite latches trigger on edge Also called master-slave latch pair

Master-Slave Register

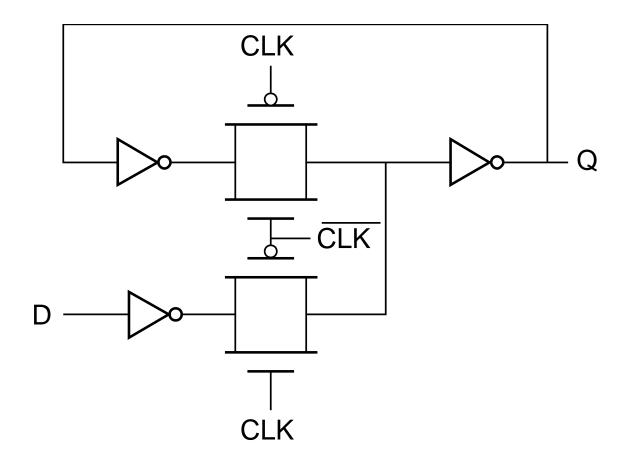

#### Multiplexer-based latch pair

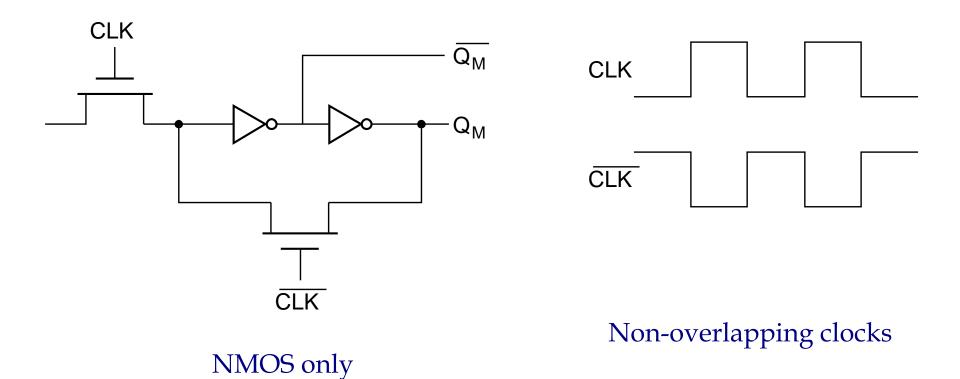

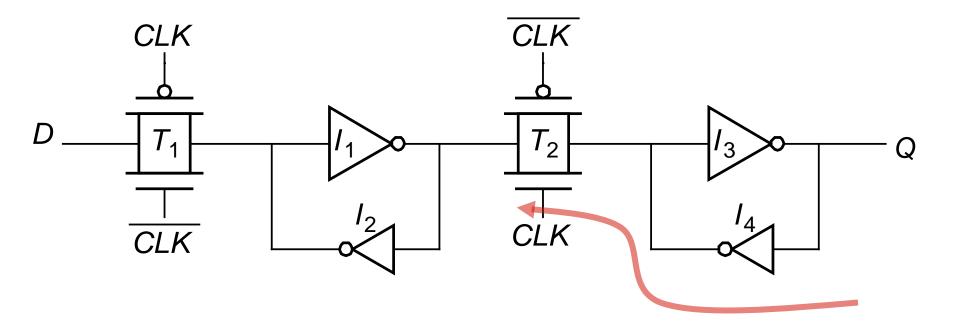

# Reduced Clock Load Master-Slave Register

## Avoiding Clock Overlap