EE 466/586 VLSI Design

Partha Pande School of EECS Washington State University pande@eecs.wsu.edu

### Lecture 26

# Semiconductor Memories

# **Semiconductor Memory Classification**

| Read-Write Memory |                                       | Non-Volatile<br>Read-Write<br>Memory | Read-Only Memory                       |

|-------------------|---------------------------------------|--------------------------------------|----------------------------------------|

| Random<br>Access  | Non-Random<br>Access                  | EPROM<br>E <sup>2</sup> PROM         | Mask-Programmed<br>Programmable (PROM) |

| SRAM<br>DRAM      | FIFO<br>LIFO<br>Shift Register<br>CAM | FLASH                                |                                        |

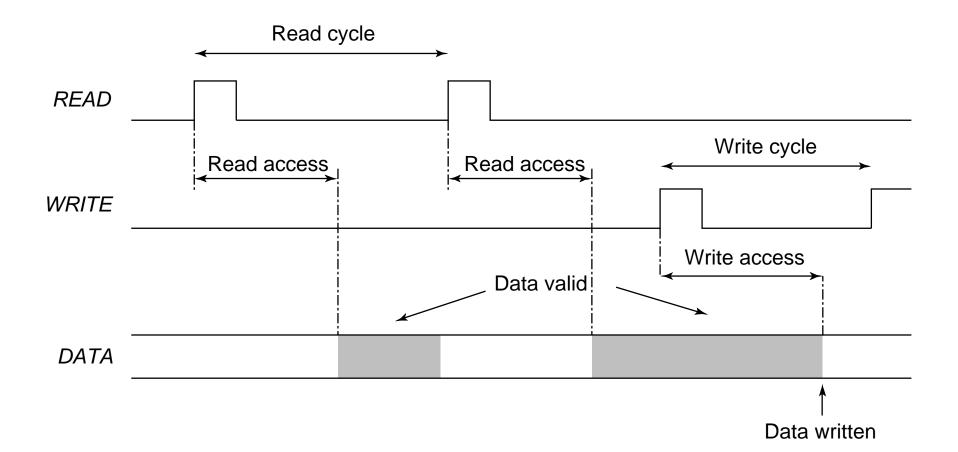

# Memory Timing: Definitions

# Memory Architecture: Decoders

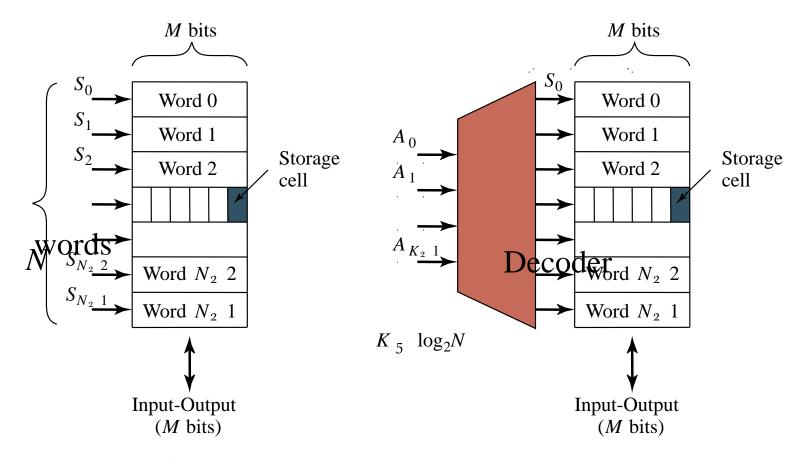

Intuitive architecture for N x M memory Too many select signals: N words == N select signals

Decoder reduces the number of select signals

$K = log_2 N$

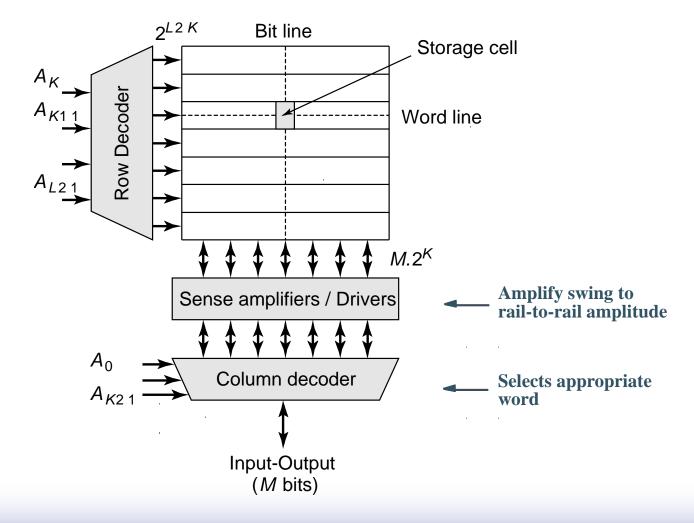

### Array-Structured Memory Architecture

#### Problem: ASPECT RATIO or HEIGHT >> WIDTH

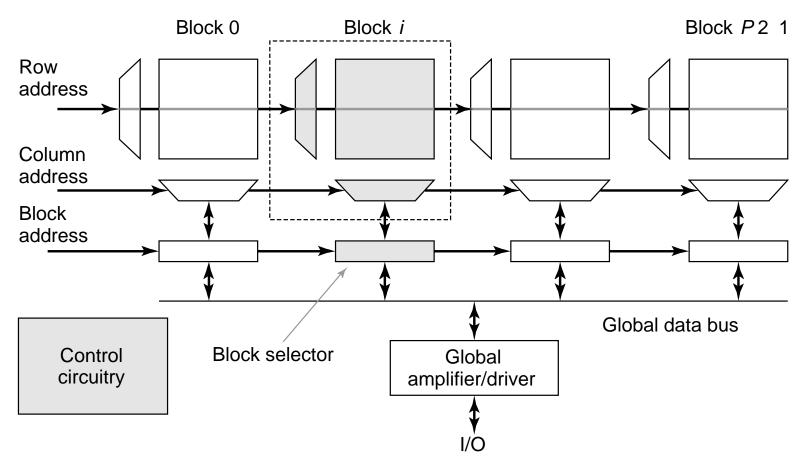

# Hierarchical Memory Architecture

#### **Advantages:**

- 1. Shorter wires within blocks

- 2. Block address activates only 1 block => power savings

## **Row Decoders**

### Collection of 2<sup>M</sup> complex logic gates Organized in regular and dense fashion

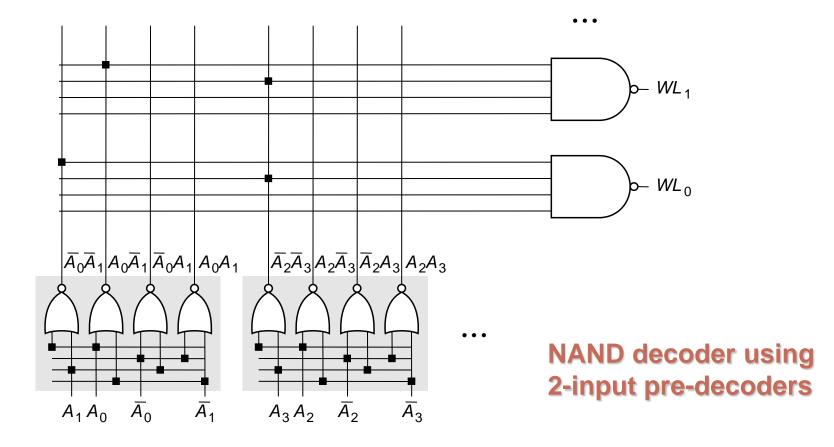

(N)AND Decoder

$$WL_{0} = A_{0}A_{1}A_{2}A_{3}A_{4}A_{5}A_{6}A_{7}A_{8}A_{9}$$

$$WL_{511} = \bar{A}_{0}A_{1}A_{2}A_{3}A_{4}A_{5}A_{6}A_{7}A_{8}A_{9}$$

#### **NOR Decoder**

$$WL_{0} = \overline{A_{0} + A_{1} + A_{2} + A_{3} + A_{4} + A_{5} + A_{6} + A_{7} + A_{8} + A_{9}}$$

$$WL_{511} = \overline{A_{0} + A_{1} + A_{2} + A_{3} + A_{4} + A_{5} + A_{6} + A_{7} + A_{8} + A_{9}}$$

### **Hierarchical Decoders**

### Multi-stage implementation improves performance

# Read-Write Memories (RAM)

□ STATIC (SRAM)

Data stored as long as supply is applied Large (6 transistors/cell) Fast Differential

DYNAMIC (DRAM)

Periodic refresh required Small (1-3 transistors/cell) Slower Single Ended

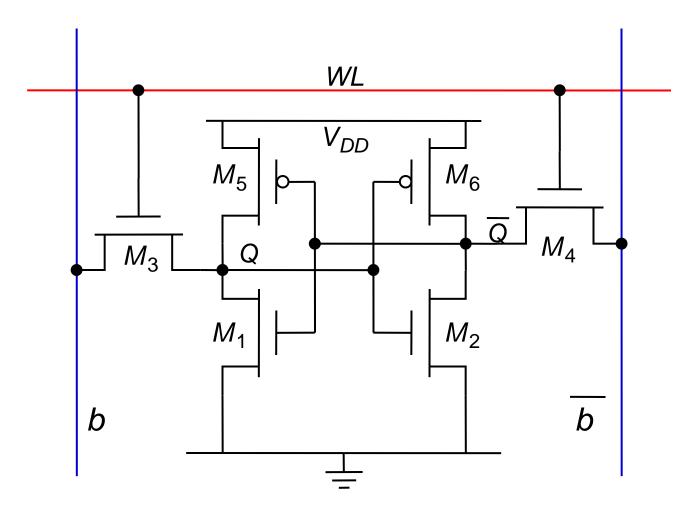

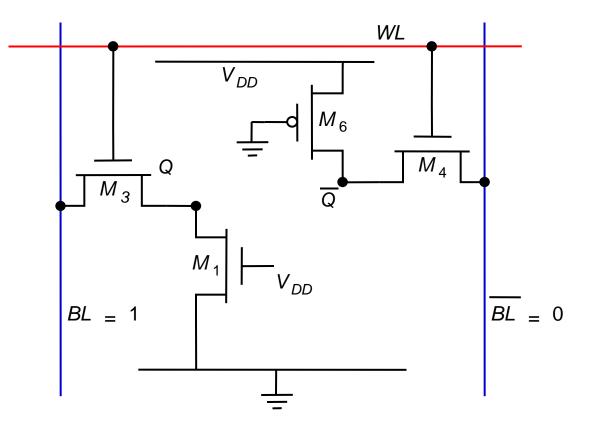

### 6-transistor CMOS SRAM Cell

# Wordline and Bitline

□ Follow board notes

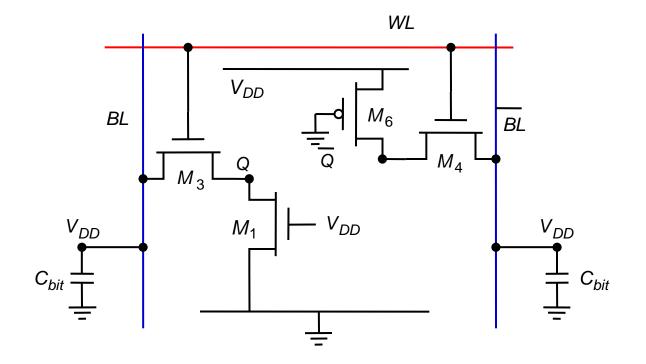

# **CMOS SRAM Analysis (Read)**

## **Read Operation**

- Assume a "0" is stored on the left side of the cell, and a "1" on the right side.

- $\square$  M<sub>1</sub> is on and M<sub>2</sub> is off.

- The row selection line is raised to V<sub>dd</sub> which turns on the access transistors

- $\Box$  Current begins to flow through M<sub>3</sub> and M<sub>1</sub>to ground.

- $\Box$  The resulting cell current slowly discharges the capacitance C<sub>bit</sub>.

- On the other side of the cell, voltage on b remains high since there is no path to ground through M<sub>2.</sub>

- $\Box$  The difference between b and b is fed to a sense amplifier

# **Read Operation**

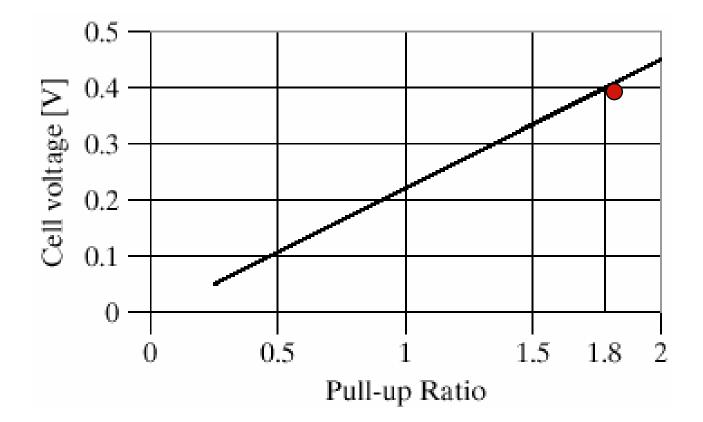

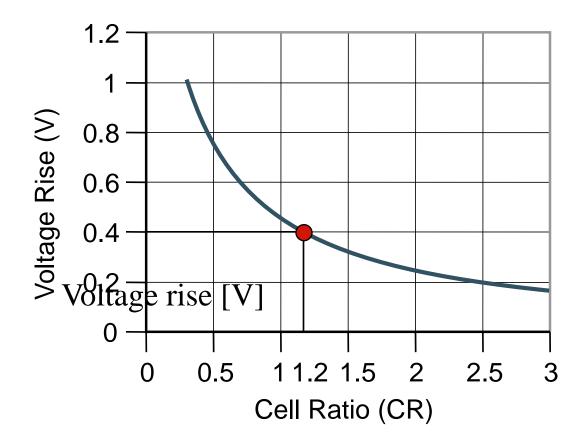

- Current flowing through M<sub>3</sub> and M<sub>1</sub>raises the output voltage at node q which could turn on M<sub>2</sub> and bring down the voltage at node q

- It should not fall below V<sub>S</sub>

- Size M<sub>3</sub> and M<sub>1</sub> appropriately.

- Make conductance of M<sub>1</sub>3 to 4 times that of M<sub>3</sub> so that the drain voltage of M<sub>1</sub>does not rise above V<sub>TN</sub>

- Cell discharge current

- Follow board notes

# **CMOS SRAM Analysis (Read)**

# **CMOS SRAM Analysis (Write)**

# Write Operation

- The operation of writing 0 or 1 is accomplished by forcing one bit line low while the other bit line remains at about V<sub>dd.</sub>

- To write 1, b is forced low, and to write 0, b is forced low

- Conditions for writing 1

- Conductance of M<sub>4</sub> is several times larger than M<sub>6</sub> so that the drain of M<sub>2</sub> is pulled below V<sub>S</sub>.

- $M_1$  turns off and its drain voltage rises to  $V_{DD}$  due to the pull up action of  $M_5$  and  $M_3$ .

- M<sub>2</sub> turns on and assists M<sub>4</sub> in pulling output q to its intended low value.

# Write Operation

- □ Size transistor pair M<sub>6</sub> and M<sub>4</sub>

- When the cell is first turned on for the write operation,

M<sub>6</sub> and M<sub>4</sub> form a pseudo-NMOS inverter.

- Current flows through the two devices and lowers the voltage at node q from its starting value of V<sub>dd</sub>

- The design of device sizes is based on pulling the node below V<sub>s</sub>

# **CMOS SRAM Analysis (Write)**