#### EE434

## **ASIC and Digital Systems**

# Midterm Exam 2

# Mar. 31, 2017. (4:10pm - 5pm)

# Instructor: Dae Hyun Kim (daehyun@eecs.wsu.edu)

#### Name:

#### WSU ID:

| Problem | Points |  |

|---------|--------|--|

| 1       | 10     |  |

| 2       | 10     |  |

| 3       | 10     |  |

| 4       | 10     |  |

| 5       | 10     |  |

| Total   | 50     |  |

\* Allowed: Textbooks, cheat sheets, class notes, notebooks, calculators, watches

\* Not allowed: Electronic devices (smart phones, tablet PCs, laptops, etc.) except calculators and watches

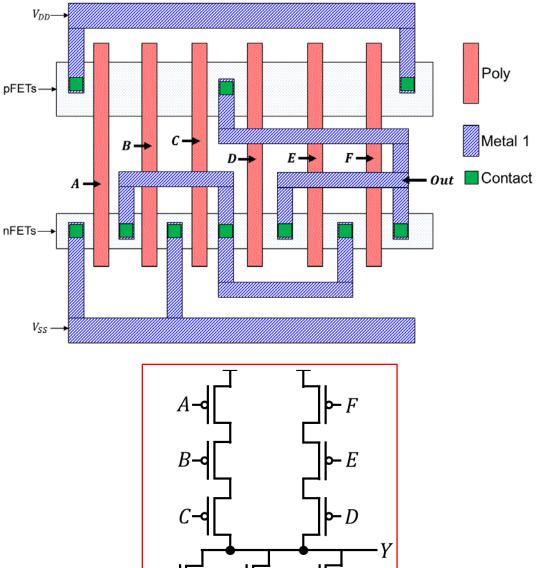

# Problem #1 (Layout, 10 points).

Represent Out as a Boolean function of A, B, C, D, E, F.

$Y = \overline{(A + B + C) \cdot (D + E + F)}$

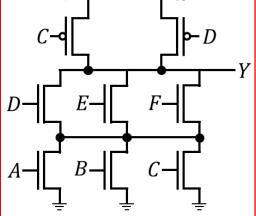

## Problem #2 (DC Characteristics, 10 points).

An infinite chain of inverters is defined as follows:

All the inverters are identical, i.e., have the same characteristics. The above chain is modeled as a block diagram as follows:

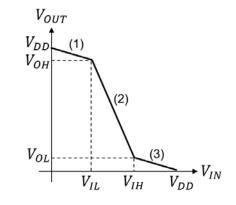

where *Noise* k is the k-th noise and *Source* is a signal generator and  $V_{Source} = V_{DD} \cdot u(t)$ (i.e., 0 if t < 0 and  $V_{DD}$  if  $t \ge 0$ ).  $V_{DD} = 1V$ . The DC characteristic of an inverter is approximated using three segments as follows (If  $V_{in} \ge V_{DD}$ ,  $V_{out} = 0$ . If  $V_{in} \le 0$ ,  $V_{out} = V_{DD}$ .):

1)

$$V_{out} = \frac{V_{OH} - V_{DD}}{V_{IL}} \cdot V_{in} + V_{DD}$$

2)

$$V_{out} = \frac{V_{OL} - V_{OH}}{V_{IH} - V_{IL}} \cdot (V_{in} - V_{IH}) + V_{OL}$$

3)

$$V_{out} = -\frac{V_{OL}}{V_{DD} - V_{IH}} \cdot (V_{in} - V_{DD})$$

Each noise source is an independent voltage signal and its range is as follows ( $V_N > 0$ ):

•

$$|V_{noise}| \leq V_N$$

<u>Compute the max. value of  $V_N$  that does not cause signal inversion for the following two</u> cases (Note: Signal inversion occurs if a signal reaches 0.5V when it should be 0 or 1):

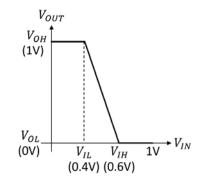

- Case 1)  $V_{OL} = 0V, V_{OH} = 1V, V_{IL} = 0.4V, V_{IH} = 0.6V$

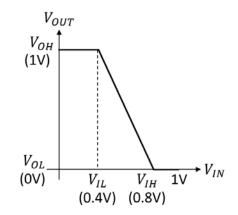

- Case 2)  $V_{OL} = 0V, V_{OH} = 1V, V_{IL} = 0.4V, V_{IH} = 0.8V$

Case 1) In this case, y = -5x + 3 in Region 2. The high noise margin is 0.4V, so is the low noise margin. Suppose  $V_N$  is  $(0.4 + \delta)V$  where  $\delta > 0$ . Let's take at a look at the worst cases.

- Input of inverter m: 1V

- Output of inverter m: 0V

- Input of inverter (m+1):  $(0.4 + \delta)V / a(n) = 0.4 + b(n)$

- Output of inverter (m+1):  $(1.0 5\delta)V // -5a(n) + 3 = 1 5b(n)$

- Input of inverter (m+2):  $(0.6 6\delta)V // -5a(n) + 2.6 \delta = 0.6 5b(n) \delta$

- Output of inverter (m+2):  $(30\delta)V // 25a(n) 10 + 5\delta = 25b(n) + 5\delta$

- Input of inverter (m+3):  $(0.4 + 31\delta)V \parallel a(n+1) = 25a(n) 9.6 + 6\delta = 0.4 + 25b(n) + 6\delta$  ->  $b(n+1) = 25b(n) + 6\delta, a(n+1) = 0.4 + b(n+1)$

- ...

a(n + 1) = 0.4 + b(n + 1) and  $b(n + 1) = 25b(n) + 6\delta$ . Since b(n) goes to infinity as n increases, so signal inversion happens.

If  $V_N$  is 0.4V

- Input of inverter m: 1V

- Output of inverter m: 0V

- Input of inverter (m+1): 0.4V

- Output of inverter (m+1): 1V

- Input of inverter (m+2): 0.6V

- Output of inverter (m+2): 0V

- Input of inverter (m+3): 0.4V

- ...

Thus, if  $\delta > 0$ , signal inversion will eventually occur no matter how small  $\delta$  is. Thus, the maximum  $V_N$  is **0.4V** in this case.

Case 2) In this case, y = -2.5x + 2 in Region 2. When the output is 0.4V, the input voltage is 0.64V. Suppose  $V_N$  is X(V) where X is between 0.2V and 0.4V. Let's take at a look at the worst cases.

- Input of inverter m: 1V

- Output of inverter m: 0V

- Input of inverter (m+1): X(V)

- Output of inverter (m+1): 1V

- Input of inverter (m+2): (1 X)V

- Output of inverter (m+2): (-0.5 + 2.5X)V

- Input of inverter (m+3): (-0.5 + 3.5X)V

If (-0.5 + 3.5X)V is greater than 0.4V, the output voltage is less than 1V, then a positive feedback loop is formed, so we solve the following inequality:

$$(-0.5+3.5X)V \leq 0.4V$$

Thus,  $\underline{V}_N \approx 0.257V$ .

# Problem #3 (Elmore Delay, 10 points).

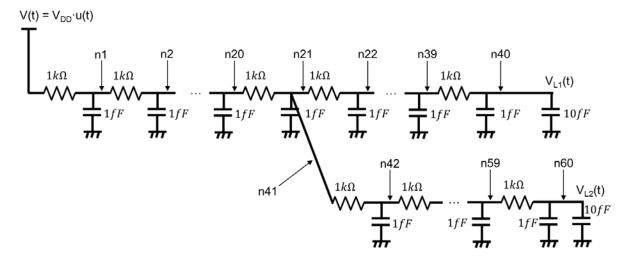

The RC tree shown below has two delay constraints as follows:

- The delay from the driver to  $V_{L1}$  should be less than or equal to 900ps.

- The delay from the driver to  $V_{L2}$  should be less than or equal to 6823ps.

Currently, the delay at  $V_{L1}$  is  $1k * 11f + 1k * 12f + \dots + 1k * 29f + 1k * 59f + 1k * 60f + \dots + 1k * 79f = 1829ps$ , so is the delay at  $V_{L2}$ .

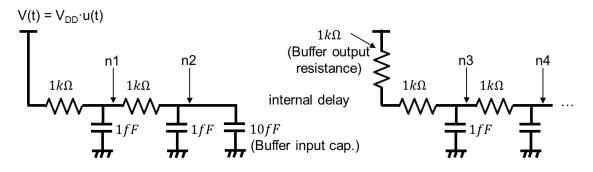

You are supposed to insert <u>only one buffer</u> in the RC tree to satisfy the delay constraints at both  $V_{L1}$  and  $V_{L2}$ . You can insert the buffer only into one of the designated nodes (n1 ~ n60). The buffer has the following characteristics:

- Input capacitance: 10 fF

- Internal delay: 20ps

- Output resistance:  $1k\Omega$

When you insert a buffer into a node, the RC tree before and after the buffer are separated as follows (assuming the buffer is inserted into n2 in the figure above):

In this case (inserting a buffer into n2), the delay at  $V_{L1}$  is  $[1k * 11f + 1k * 12f + \dots + 1k * 29f + 1k * 59f + 1k * 60f + \dots + 1k * 77f + 1k * 77f] + [20ps] + [1k * 11f + 1k * 12f] = (1749 + 20 + 23)ps = 1792ps$ , so is the delay at  $V_{L2}$ . As you see, the delay is reduced from 1829ps to 1792ps.

Insert a buffer into one of the nodes ( $n1 \sim n60$ ) so that it satisfies the delay constraints at both  $V_{L1}$  and  $V_{L2}$ . Then, compute the Elmore delay at  $V_{L1}$ .

(Help: The sum of a, a + 1, a + 2, ..., n is  $\frac{(n+a)(n-a+1)}{2}$ . For example,  $5 + 6 + \dots + 10 = \frac{(10+5)(10-5+1)}{2} = 45$ .)

If I insert a buffer into node n21, the delay at  $V_{L1}$  is

$$(1k * 11f + 1k * 12f + \dots + 1k * 29f + 1k * 29f) + (20ps) + (1k * 40f + 1k * 41f + \dots + 1k * 60f) = (380ps + 29ps) + (20ps) + (1050ps) = 1479ps$$

If I insert a buffer into node n41, the delay at  $V_{L1}$  is

$$(1k * 11f + 1k * 12f + \dots + 1k * 29f) + (1k * 40f + 1k * 41f + \dots + 1k * 60f) = (380ps) + (1050ps) = 1430ps$$

If I insert a buffer into node n20, the delay at  $V_{L1}$  is

$$\begin{aligned} (1k*11f + 1k*12f + \dots + 1k*29f) + (1k*59f) + (1k*59f) + (20ps) \\ &+ (1k*11f + 1k*12f + \dots + 1k*30f) \\ &= (380ps) + (59ps) + (59ps) + (20ps) + (410ps) = \textbf{869ps} \end{aligned}$$

If I insert a buffer into node n19, the delay at  $V_{L1}$  is

$$(1k * 11f + 1k * 12f + \dots + 1k * 29f) + (1k * 59f) + (1k * 60f) + (1k * 60f) + (20ps) + (1k * 11f + 1k * 12f + \dots + 1k * 29f) = (380ps) + (59ps) + (60ps) + (20ps) + (380ps) = 899ps$$

Node: n20 or n19

Elmore delay at  $V_{L1}$ : 869ps or 899ps

## Problem #4 (Pseudo-nMOS, 10 points).

Draw a pseudo-nMOS schematic for  $Y = \overline{A \cdot B \cdot C + (D + E) \cdot F}$  and properly size the nFETs to achieve the following output level for logic output 0:

•

$$V_{out} \leq 0.1 V_{DD}$$

Use the following parameters:

- Resistance of a 1 × nFET = Resistance of a 2 × pFET

- The size of the pFET:  $4 \times$

- Do not use the transistor-mode-based computation for sizing. You can just use the resistance values for sizing.

- Do not oversize the nFETs.

The resistance of the pFET is  $R_n/2$  where the resistance of a 1X nFET is  $R_n$ . Suppose the resistance of an nFET path is  $R_k$ . Then,  $\frac{R_k}{\binom{R_n}{2} + R_k} \leq 0.1$ , so  $R_k \leq \frac{1}{18}R_n$ .

For A=B=C=1:

$$3 \cdot R = \frac{1}{18}R_n \implies R = \frac{1}{54}R_n \implies A = B = C = 54 \times C$$

For F=1 and (D or E=1):

$$2 \cdot R = \frac{1}{18}R_n \implies R = \frac{1}{36}R_n \implies D = E = F = 36 \times$$

$$0 - 4X = \frac{R_n}{2}$$

$$A - 54X$$

$$F - 36X$$

$$B - 54X$$

$$C - 54X$$

$$D - 36X$$

$$E - 36X$$

$$E - 36X$$

$$E - 36X$$

### Problem #5 (Capacitive Coupling, 10 points).

The following figure models the coupling effect between two adjacent wires.

$$V_{s}(t) = V_{DD} \cdot u(t) \underbrace{\bigcap_{\prime \prime \prime \prime}}_{\prime \prime \prime \prime} \underbrace{C \frac{1}{1}}_{\prime \prime \prime \prime} V_{c} \underbrace{\frac{1}{1}}_{\prime \prime \prime \prime} C_{L}$$

$V_1(t)$  is an aggressor and  $V_2(t)$  is a victim.  $V_2(t)$  is as follows:

$$V_{2}(t) = \frac{V_{DD}}{2} \left[ e^{-\frac{t}{\tau_{1}}} - e^{-\frac{t}{\tau_{2}}} \right] u(t)$$

where

•

$$\tau_1 = R(C + C_L + 2C_C)$$

•

$$\tau_2 = R(C + C_L)$$

In this case, the max. value of  $V_2(t)$  is found by differentiating  $V_2(t)$  with respect to t. The max. value occurs when t is

$$t_{max} = \frac{R(C + C_L)(C + C_L + 2C_C)}{2} \cdot \ln \frac{C + C_L + 2C_C}{C + C_L}$$

and the max. value of  $V_2(t)$  is

$$V_{2,max} = \frac{V_{DD}}{2} \cdot \left(1 - \frac{\tau_2}{\tau_1}\right) \cdot \left(\frac{\tau_2}{\tau_1}\right)^{\frac{\tau_2}{2RC_c}}$$

Answer the following questions (Hint: Use the above formula or your intuition to solve this problem):

- If C<sub>c</sub> increases, V<sub>2,max</sub> increases. (True/False)

- If C increases, V<sub>2,max</sub> increases. (True/False)

- If C<sub>L</sub> increases, V<sub>2,max</sub> increases. (True/False)

- If *R* increases, *V*<sub>2,max</sub> increases. (True/False)

- The max. value of  $V_2(t)$  can be greater than  $V_{DD}/2$ . (True/False)

(Hint:

$$\lim_{x \to \infty} \left(\frac{1}{x}\right)^{\frac{1}{x}} = 1$$

.  $\lim_{x \to \infty} \left(\frac{x}{x+c}\right)^{\frac{x}{c}} = e$ .  $\left(\frac{x}{x+c}\right)^{\frac{x}{c}} > 1$ . (when  $c > 0$ ))

$$V_{2,max} = \frac{V_{DD}}{2} \cdot \left(1 - \frac{C + C_L}{C + C_L + 2C_C}\right) \cdot \left(\frac{C + C_L}{C + C_L + 2C_C}\right)^{\frac{C + C_L}{2C_C}}$$

$\left(1-\frac{c+c_L}{c+c_L+2c_c}\right)=a, \frac{c+c_L}{c+c_L+2c_c}=b, \text{ and } \frac{c+c_L}{2c_c}=d.$

- If  $C_c$  increases, *a* approaches 1 and *b* and *d* approach 0, so  $b^d$  approaches 1. Thus,  $V_{2,max}$  increases (approaches  $\frac{V_{DD}}{2}$ ).

- If *C* increases, *a* approaches 0 and *b*<sup>*d*</sup> approaches *e*, so *V*<sub>2,max</sub> decreases (approaches 0).

- C<sub>L</sub> and C are interchangeable, so if C<sub>L</sub> increases, V<sub>2,max</sub> decreases (approaches 0).

- $V_{2,max}$  does not include R, so it does not increase even if R increases.

- *a* is less than 1.  $b^d$  is less than 1. Thus,  $V_{2,max}$  is less than  $V_{DD}/2$ .