Lab 3 (Due 4:10pm, Apr. 27<sup>th</sup>)

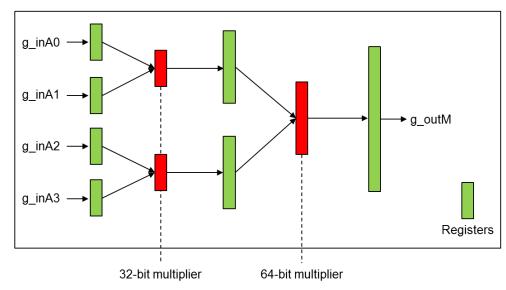

Design a four-input 32-bit pipelined multiplier. The following shows a block diagram for the multiplier:

The following file also contains all the files required for lab3.

- http://eecs.wsu.edu/~ee434/Labs/lab3.tar.gz

- pmul32\_4\_fm.globals, .view, .v, .sdc, .ctstch (use metalfill.cmd for metal fill insertion)

## **Spec**

• Initial core utilization: 0.5

## **Submit**

- Layout snapshots at each stage

- o After P/G network design

- o After placement (turn off the visibility of all metal layers)

- o After routing (turn off the visibility of all metal layers)

- o After routing (turn on the visibility of all metal layers)

- o After fill insertion (turn on the visibility of all metal layers)

- Timing report (use "timeDesign") at each stage

- o After placement

- o After pre-CTS optimization

- o After CTS

- o After post-CTS optimization

- o After routing

- o After post-routing optimization

- After fill insertion