### EE434 ASIC & Digital Systems

#### Active-HDL

Dae Hyun Kim daehyun@eecs.wsu.edu

# **Download**

- http://www.aldec.com

- PRODUCTS  $\rightarrow$  Active-HDL  $\rightarrow$  Free Evaluation

- (requires registration)

### How to Run Active-HDL

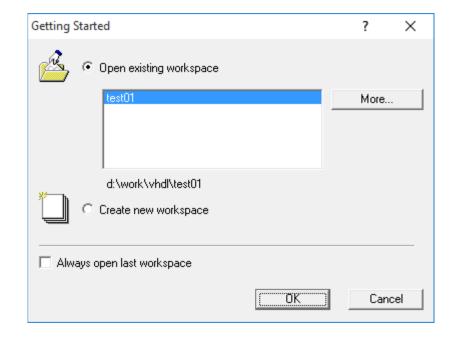

• Run your Active-HDL and you will see the following screen.

# How to Run Active-HDL

- If you want to open an existing workspace, select it and click OK.

- If you want to create a new workspace, select "Create new workspace" and click OK.

| Getting Started      |                            |    | ? | ×      | ( |

|----------------------|----------------------------|----|---|--------|---|

| 🙆 O Open exis        | ing workspace              |    |   |        |   |

| test01               |                            |    | M | ore    |   |

| d:\work\             | vhdl\test01<br>v workspace |    |   |        |   |

| 🗖 Always open last w | orkspace                   |    |   |        |   |

|                      |                            | ОК |   | Cancel |   |

### **Create a New Workspace**

- Type the workspace name.

- Turn on "Add New Design to Workspace.

- Click OK.

| Type the workspace name:                   |                |

|--------------------------------------------|----------------|

| test02                                     |                |

| Select the location of the wor             | kspace folder: |

| c:\my_designs\                             |                |

|                                            | Browse         |

| <ul> <li>Add New Design to Work</li> </ul> | space          |

### **Create a New Workspace**

- In the "New Design Wizard" window, select "Create an Empty Design" and click Next.

- If you see a "Property Page" window, just click Next.

- In the "New Design Wizard" window, type a design name and click Next (see the next slide).

### **Create a New Workspace**

| w Design Wizard                                                   | × |

|-------------------------------------------------------------------|---|

| Specify basic information about the new design.                   |   |

| Type the design name:                                             |   |

| myLogic                                                           |   |

| Select the location of the design folder:                         |   |

| c:\My_Designs\test02                                              |   |

| Browse.                                                           |   |

|                                                                   |   |

|                                                                   |   |

| The name of the default working library of the design:            |   |

| The name of the default working library of the design:<br>myLogic | _ |

|                                                                   |   |

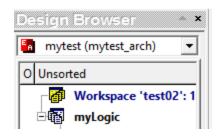

# **Design Browser**

• You will see a design browser window in the left.

### Add a New File to the Design

- Click File  $\rightarrow$  New  $\rightarrow$  VHDL Source.

- Or double-click "Add New File" in the design browser to add a new file to the existing design.

- I am creating and adding "myInv.vhd" to my design.

| A | dd New File            |               |               |                              | ?            | $\times$ |

|---|------------------------|---------------|---------------|------------------------------|--------------|----------|

|   | Empty Files W          | /izards       |               |                              |              |          |

|   |                        | ‡ <b>-</b>    |               |                              |              |          |

|   | VHDL Source<br>Code    | Block Diagram | State Diagram | SystemVerilog<br>Source Code |              | irce     |

|   | <                      |               |               |                              |              | >        |

|   | New Empty Fil<br>Name: | le:           |               |                              |              |          |

|   | mylnv.vhd              |               |               |                              |              |          |

|   |                        |               |               |                              | Add Existing | File     |

|   |                        |               |               | ОК                           | Can          | cel      |

# Add a New File to the Design

- I successfully created and added "myInv.vhd" to myLogic.

- The ? Symbol in front of the file name means that it's not been compiled.

# **Edit and Compile**

Add the following code to myinv.vhd.

```

1 LIBRARY IEEE;

2 USE IEEE.std_logic_1164.ALL;

3

4 ENTITY myInv_X1 IS

5 PORT ( a : IN std_logic;

6 zn : OUT std_logic );

7 END myInv_X1;

8

9 ARCHITECTURE myInv_X1_arch OF myInv_X1 IS

10 BEGIN

11 zn <= NOT a;

12 END myInv_X1;

13

```

- Save and compile.

- To compile the design, click Design  $\rightarrow$  Compile or click the compile icon.

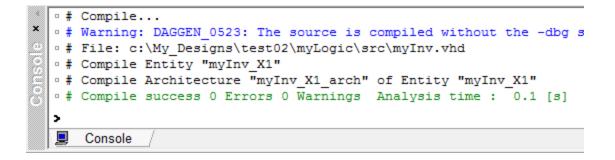

# **System Messages**

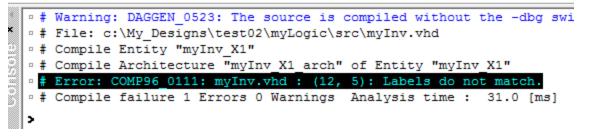

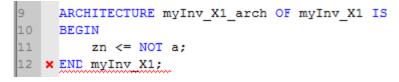

In the bottom of the Active-HDL window, you will see an error message as follows:

- This means that something is wrong in the 12<sup>th</sup> line, 5<sup>th</sup> character.

- Double-click the error message to directly go to the problematic line.

# Debugging

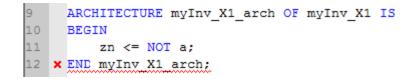

• Fix the error as follows:

• Compile the design again.

• There is no error.

### Testbench

• Double-click "Add New File" to add one more file.

| Add New File                                                                                  | ?            | $\times$ |

|-----------------------------------------------------------------------------------------------|--------------|----------|

| Empty Files Wizards                                                                           |              |          |

|                                                                                               |              |          |

| VHDL Source Block Diagram State Diagram SystemC SystemVerilog<br>Code Source Code Source Code |              | rce      |

| <                                                                                             |              | >        |

| New Empty File:<br>Name:                                                                      |              |          |

| myLogic_tb.vhd                                                                                |              |          |

|                                                                                               | Add Existing | File     |

| ОК                                                                                            | Can          | cel      |

### **Testbench**

• Now, I am going to test the inverter I made. To test it, I need an entity. Type the following into myLogic\_tb.vhd and compile it.

```

LIBRARY IEEE;

USE IEEE.std logic 1164.ALL;

3

ENTITY myTest IS

END myTest;

ARCHITECTURE myTest arch OF myTest IS

COMPONENT myInv X1

9

PORT ( a : IN std logic;

zn : OUT std logic );

11

END COMPONENT:

12

SIGNAL g in : std logic;

13

SIGNAL g out : std logic;

14

BEGIN

15

u1 : myInv_X1 PORT MAP ( a => g_in, zn => g_out );

16

PROCESS

17

BEGIN

18

WAIT FOR 1ns;

19

g in <= '0';

WAIT FOR 1ns;

21

g in <= '1';

22

WAIT FOR 1ns;

23

g in <= '0';

24

END PROCESS:

25

END mvTest arch:

```

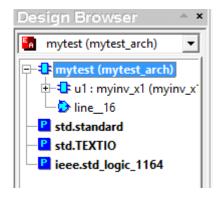

- First, you should choose the topmost-level module you want to run in the design browser.

- Select myTest in the design browser as follows.

- Initialize your simulation.

- Click Simulation  $\rightarrow$  Initialize Simulation.

Now, you will see entities instead of files in the design browser as follows:

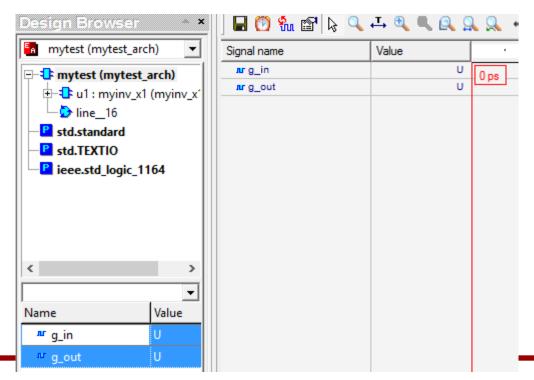

- A simple way to check the functionality of the inverter is to look at the waveform of the output.

- Open a waveform window.

- Click the "New waveform" icon.

- Add the signals you want to see.

- I want to check both the input and output.

- Click "myTest" in the design browser and drag&drop the two signals (g\_in and g\_out) into the waveform window.

- Simulate until 5ns.

- − Click the "Run Until" icon ≥ and type 5ns and click OK.

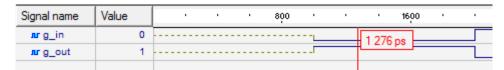

- The following shows my waveform window.

| Signal name     | Value  | •    | • | 800 | • | • | • | 1600 | • | • | • | 2400 | • | • | • | 3200 | • | • | • | 40,00 | • | • | • | 48,00 |      |

|-----------------|--------|------|---|-----|---|---|---|------|---|---|---|------|---|---|---|------|---|---|---|-------|---|---|---|-------|------|

| <b>ச</b> g_in   | 0 to 1 | <br> |   |     |   |   |   |      |   |   |   |      |   |   |   |      |   |   |   |       |   |   |   |       | 5 ns |

| <b>л</b> rg_out | 1 to 0 | <br> |   |     |   |   |   |      |   |   |   |      |   |   |   |      |   |   |   |       |   |   |   |       |      |

|                 |        |      |   |     |   |   |   |      |   |   |   |      |   |   |   |      |   |   |   |       |   |   |   |       |      |

- Analysis

- Initially, the input and output are unknown (U). Click somewhere between 0 and 1ns and check their values.

| Signal name         | Value |   | •    | •     | 800      | • | • |

|---------------------|-------|---|------|-------|----------|---|---|

| <mark>ஸ</mark> g_in | L     | J | <br> | 467 p |          |   |   |

| <b>л</b> rg_out     | L     | J | <br> |       | <u> </u> |   |   |

|                     |       |   |      |       |          |   |   |

- It is correct because we didn't initialize the input.

• At 1ns, we set g\_in to 0, so we get 1 at the output.

• At 2ns, we set g\_in to 1, so we get 0 at the output.

| Signal name         | Value | •    | • | 800 | • | • | • | 1600 | • | • | • | 2400 | •    | • | • | 3200 |

|---------------------|-------|------|---|-----|---|---|---|------|---|---|---|------|------|---|---|------|

| <mark>ஸ</mark> g_in | 1     | <br> |   |     |   |   |   |      |   |   |   | 2.34 | 1 ns |   |   |      |

| nr g_out            | 0     | <br> |   |     |   |   |   |      |   |   |   | 20.  |      |   |   |      |

|                     |       |      |   |     |   |   |   |      |   |   |   |      |      |   |   |      |

- Finish your simulation.

- Click the "End simulation" icon.