# EE434 ASIC & Digital Systems

ModelSim

Dae Hyun Kim daehyun@eecs.wsu.edu

#### Connect to the EE434 Server

- ssh1.eecs.wsu.edu

- ssh2.eecs.wsu.edu

- ssh3.eecs.wsu.edu

- ssh4.eecs.wsu.edu

- Create a directory.

- mkdir ee434\_hdl

- Change to the new directory.

- cd ee434\_hdl

#### Run ModelSim

- Source the following file (you should source this file whenever you newly connect to the servers):

- source /net/ictools/sh/mentor-modelsim.sh

- Run ModelSim

- vsim

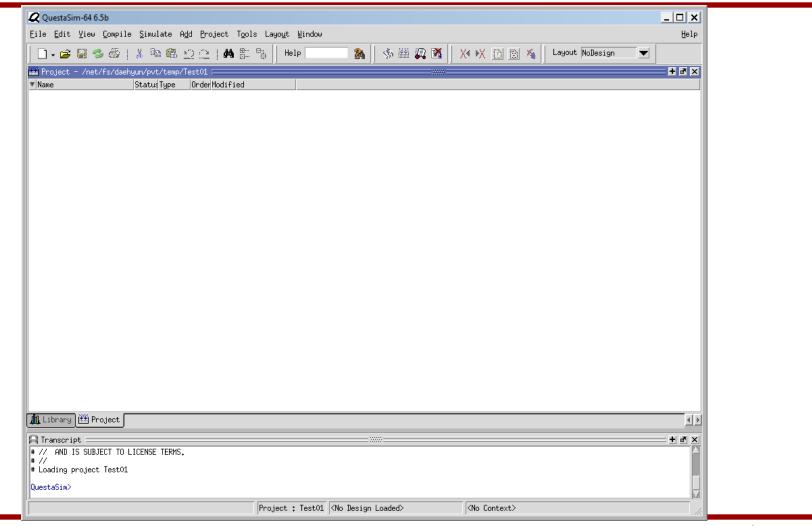

## **Main Window**

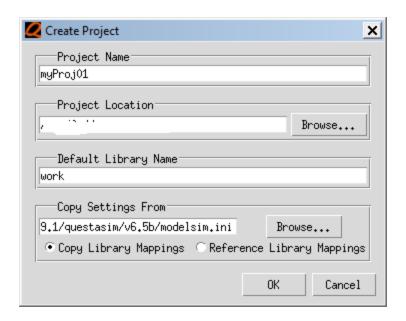

## **Create a New Project**

Click File → New → Project.

- Enter a project name and click OK.

- If you see a "Add items to the Project" window, close it.

## **Project & Library**

- Now, you have just made a project.

- Click the "Library" tab to see the list of libraries included in the project.

- Your work library is "work".

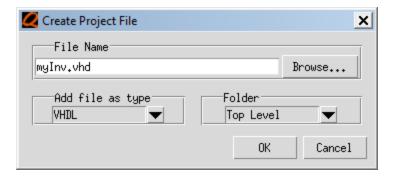

## Add a New File to Your Project

- Click the "Project" tab.

- Right-click → Add to Project → New File

- Enter mylnv.vhd in the file name and click OK.

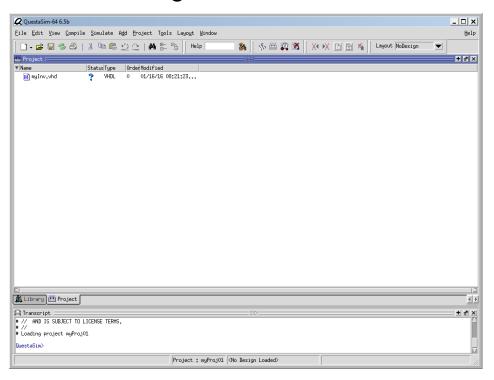

## Add a New File to Your Project

You will see the following screen.

Double-click mylnv.vhd to open it.

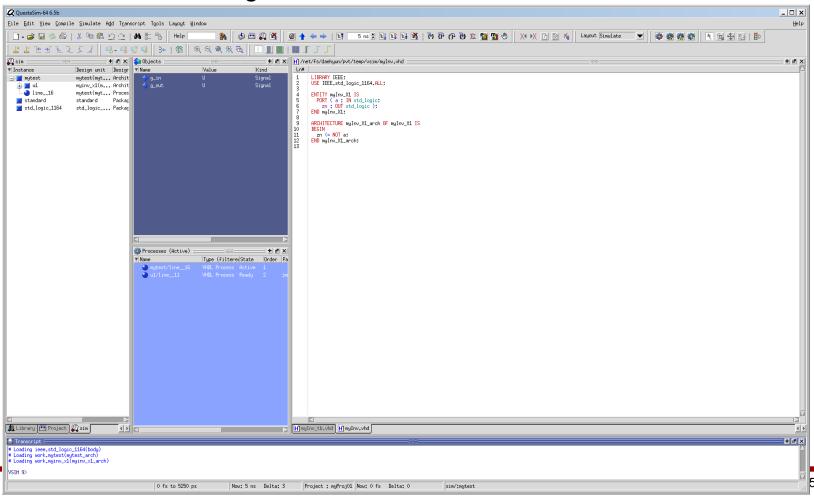

## **Edit and Compile**

Add the following code to mylnv.vhd.

```

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY myInv_X1 IS

PORT ( a : IN std_logic;

zn : OUT std_logic );

END myInv_X1;

ARCHITECTURE myInv_X1_arch OF myInv_X1 IS

BEGIN

zn <= NOT a;

END myInv_X1;

END myInv_X1;

```

- Save and compile.

- To compile the design, click Compile → Compile All or click the compile icon.

## **System Messages**

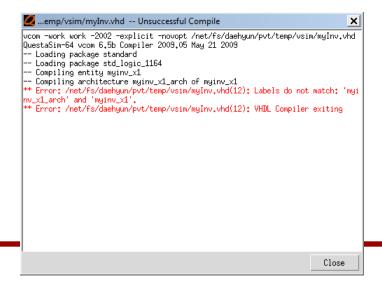

In the bottom of your ModelSim window, you will see an error message as follows:

```

# Compile of myInv.vhd failed with 1 errors.

QuestaSim>

```

- Double-click the error message and you will see a window showing detailed error messages.

- This means that something is wrong in the 12<sup>th</sup> line.

## **Debugging**

• Fix the error as follows:

```

9 ARCHITECTURE myInv_X1_arch OF myInv_X1 IS

10 BEGIN

11 zn <= NOT a;

12 x END myInv X1 arch;

```

Compile the design again.

```

# Compile of myInv.vhd was successful.

QuestaSim>

```

There is no error.

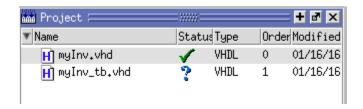

### **Testbench**

In the project window, add a new file named "myInv\_tb.vhd".

The "V" symbol means that it's been compiled correctly.

### **Testbench**

Now, I am going to test the inverter I made. To test it, I need an

entity. Type the following into myLogic\_tb.vhd and compile it.

```

Ln#

LIBRARY IEEE:

1

USE IEEE.std_logic_1164.ALL;

ENTITY myTest IS

END myTest;

ARCHITECTURE myTest_arch of myTest IS

COMPONENT myInv_X1

PORT ( a : IN std_logic; zn : OUT std_logic );

END COMPONENT:

11

SIGNAL g_in : std_logic;

12

SIGNAL g_out : std_logic;

13

BEGIN

14

u1 : myInv_X1 PORT MAP (a \Rightarrow g_in, zn \Rightarrow g_out);

15

PROCESS:

16

BEGIN

17

WAIT FOR 1 ns:

18

g_in <= '0';

19

WAIT FOR 1 ns;

20

g_in <= '1';

21

WAIT FOR 1 ns;

22

g_in <= '0':

23

END PROCESS:

24

END myTest_arch;

```

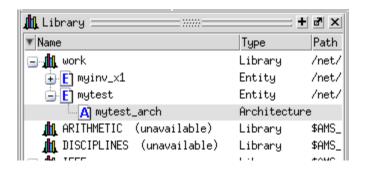

- Click the Library tab.

- Expand the "work" library.

Right-click "mytest\_arch" and choose "Simulate".

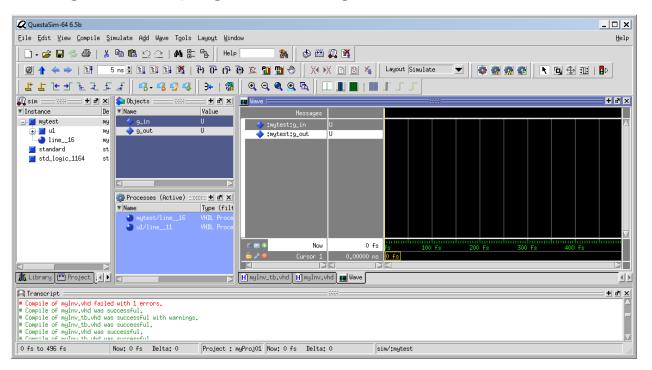

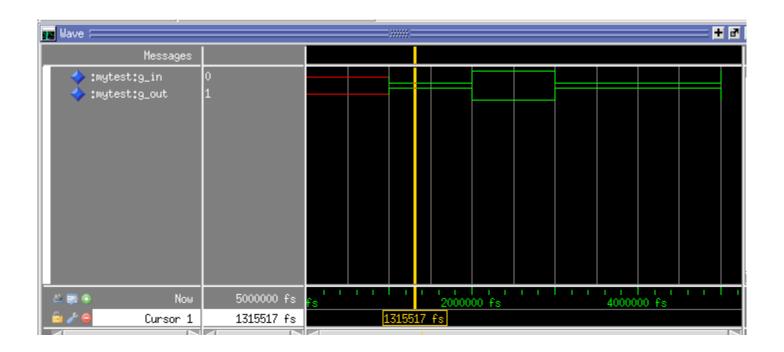

See the following window.

- Add a waveform window.

- Click View → Wave.

- Then, drag and drop "g\_in" and "g\_out" to the waveform.

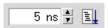

Enter "5ns" in the Run Length window and click the Run icon.

Click the waveform window and press "F" to zoom full.

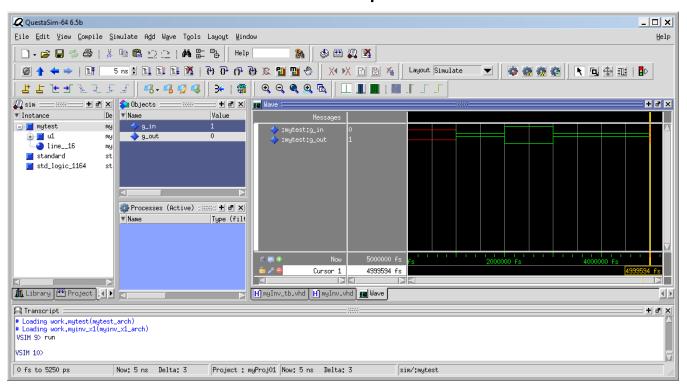

- Analysis

- Initially, the input and output are unknown (U). Click somewhere between 0 and 1ns and check their values.

It is correct because we didn't initialize the input.

At 1ns, we set g\_in to 0, so we get 1 at the output.

- Finish your simulation.

- Simulate → End Simulation.