# EE434 ASIC & Digital Systems

From Layout to SPICE Simulation (Virtuoso, Calibre, HSpice)

Spring 2016

Dae Hyun Kim

daehyun@eecs.wsu.edu

## **Preparation for Lab2**

- Download the following file into your working directory.

- wget http://eecs.wsu.edu/~ee434/Labs/lab2.tar.gz

- Unzip it.

- tar xvfz lab2.tar.gz

#### **Files**

- Shortcuts

- common\_bindkeys.il

- leBindKeys.il

- schBindKeys.il

- sh

- Files to source

- Tech file

- tech\_ng45nm.tf

- Display resource file

- display.drf

- rules

- layer.inc

- calibreDRC.rul

- calibreLVS.rul

- calibrexRC.rul

- myInv\_X1\_LVS.sp: A netlist for LVS

- myInv\_X1\_simul.sp: A netlist to simulate an inverter with parasitic RC.

- myInv\_X1\_noRC\_simul.sp: A netlist to simulate an inverter without parasitic RC.

## What We Are Going To Do

- 1. Layout

- 2. DRC

- 3. LVS

- 4. xRC

- 5. SPICE simulation

#### **How to Launch Virtuoso**

- Source the following file:

- > source sh/cadence-ic.sh

- Run Virtuoso

- > virtuoso

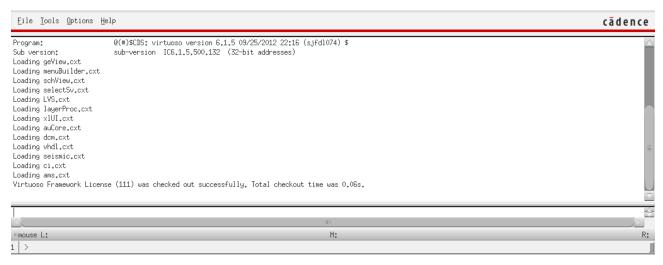

- You will see a Cadence logo and a main window (Command Interpreter Window, CIW) as follows:

### **Create a Library**

- In CIW

- Click "Tools" → "Technology File Manager...".

- In the Technology Tool Box window

- Click "New...".

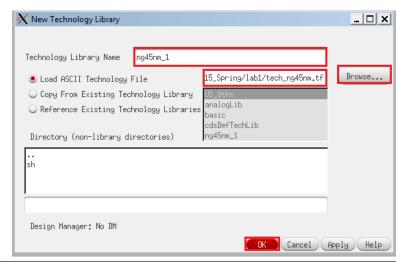

- In the New Technology Library window

- Enter a library name you want.

- Click "Browse..." to load tech\_ng45nm.tf.

- Click OK.

- You will see the following message.

## **Create a Library**

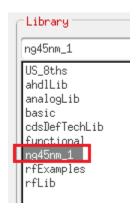

- Close the Technology Tool Box window.

- In CIW, click Tools → Library Manager ...

- In the leftmost column, you will see both your library and some default libraries.

#### **How to Create a Cell**

- In the Library Manager window, click File → New → Cell View.

- Enter a cell name and click OK.

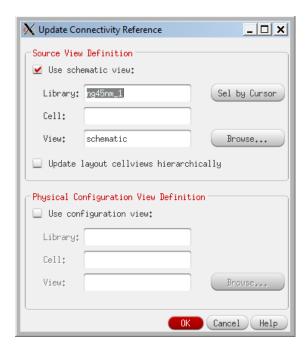

#### **How to Create a Cell**

If the following window pops up, uncheck the "Use schematic view:" and click OK.

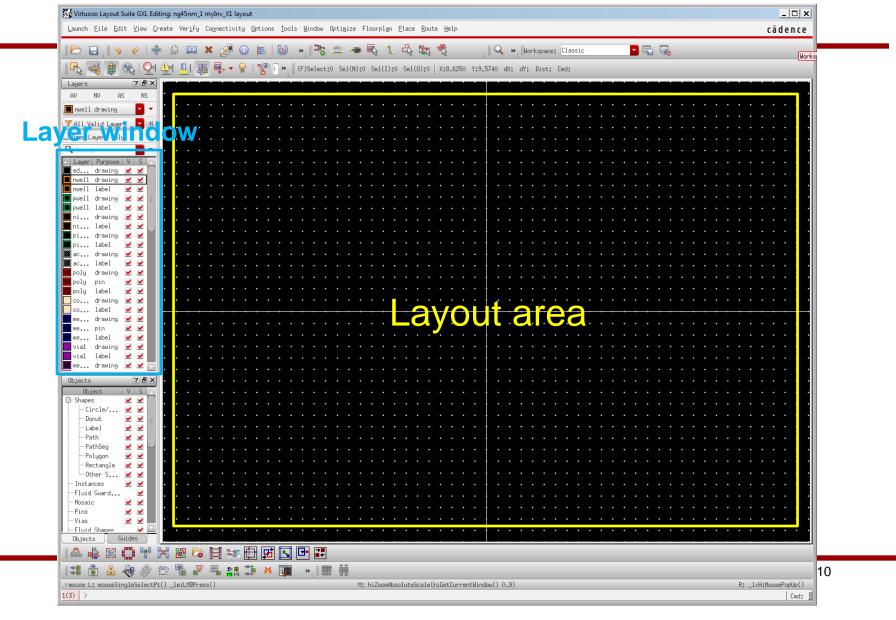

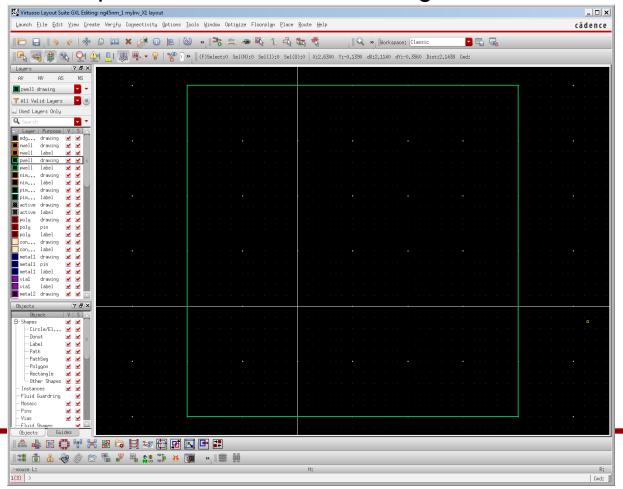

# **Layout Window**

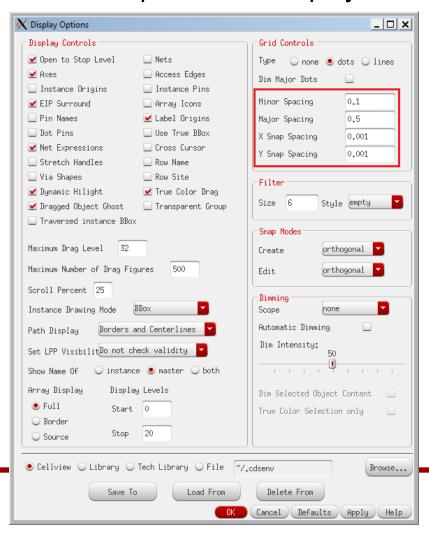

### **Editor Setup**

Press "e" or click "Options" → "Display...". Use the following

setting.

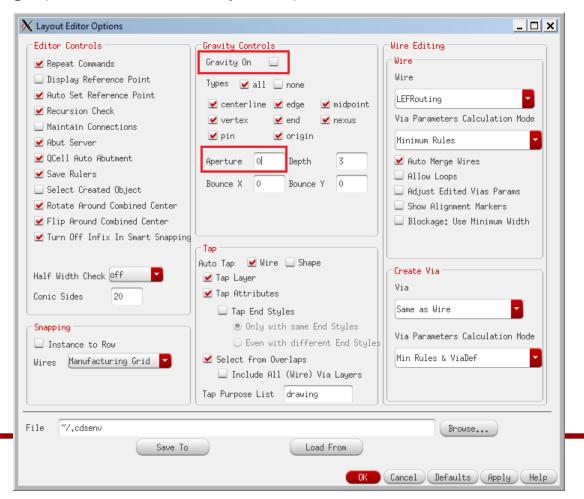

## **Editor Setup**

Press "Shift+e" or click "Options" → "Editor...". Use the following setting. (Turn off "Gravity On").

- Use the right mouse button to zoom in.

- Choose a layer you want to draw in the layer window.

- Choose "drawing" for the "Purpose".

- Press "r" or Click "Create" → "Shape" → "Rectangle". Now you are ready to draw a rectangle of the layer you selected.

- Draw a rectangle by clicking the left mouse button twice.

- Press "ESC" to stop drawing rectangles.

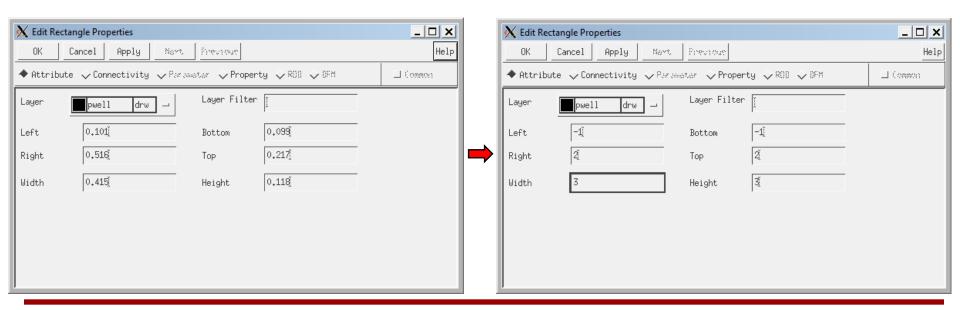

- Click the rectangle you just drew.

- Press "q" to see the property of the rectangle.

- You can fine-control the coordinates in this window.

- Click "OK" to accept the change.

- Press "f" to zoom out.

- Click whitespace to unselect the rectangle.

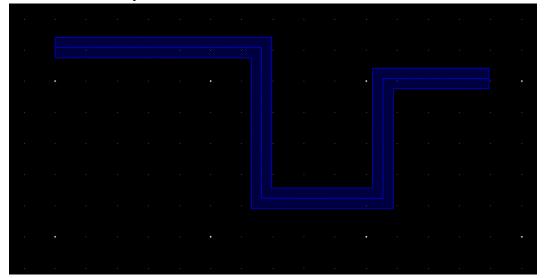

- Drawing wires using rectangles is pretty painful.

- Click "metal 1 drawing" in the layer window.

- Press "p" or click "Create" → "Shape" → "Path".

- Now you are ready to draw a path of metal 1. Its width is predefined in the technology file.

- Try to draw some paths. To finish, double click the left button.

- Move: choose an object, press "m", and move it. Or, click whitespace to unselect, press "m", and click and move an object.

- Copy: Click whitespace to unselect, press "c", click the object you want to copy, and paste it.

- Stretch: click whitespace to unselect. Press "s" and stretch a boundary of an object.

- Ruler: press "k".

- Clear ruler: shift+k.

- Merge: select two objects of the same type crossing each other and press "shift+m". It will create a polygon object.

- Save: F2

- See the following page:

- http://www.eda.ncsu.edu/wiki/FreePDK45:Contents

- Click each layer under "Design Rules".

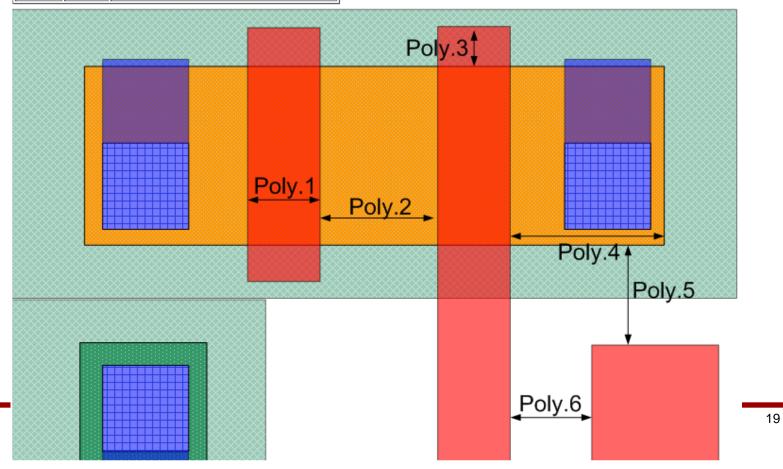

#### FreePDK45:PolyRules

| Rule   | Value  | Description                             |

|--------|--------|-----------------------------------------|

| POLY.1 | 50 nm  | Minimum width of poly                   |

| POLY.2 | 140 nm | Minimum spacing of poly AND active      |

| POLY.3 | 55 nm  | Minimum poly extension beyond active    |

| POLY.4 | 70 nm  | Minimum enclosure of active around gate |

| POLY.5 | 50 nm  | Minimum spacing of field poly to active |

| POLY.6 | 75 nm  | Minimum Minimum spacing of field poly   |

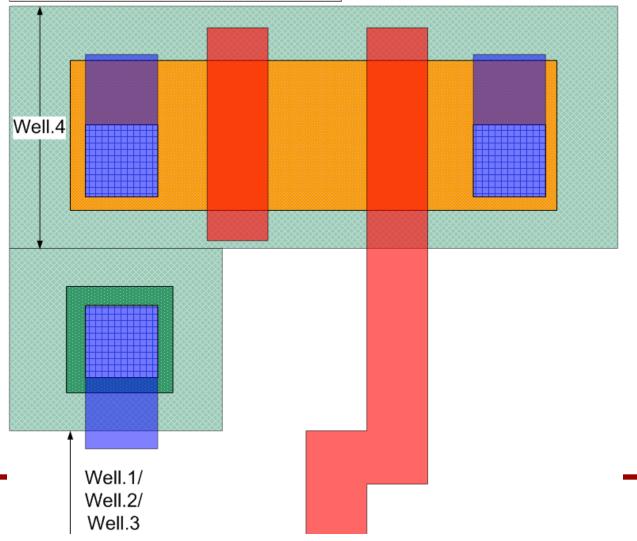

#### FreePDK45:WellRules

| Rule   | Value  | Description                                           |

|--------|--------|-------------------------------------------------------|

| WELL.1 | none   | saveDerived: nwell/pwell must not overlap             |

| WELL.2 | 225 nm | Minimum spacing of nwell/pwell at different potential |

| WELL.3 | 135 nm | Minimum spacing of nwell/pwell at the same potential  |

| WELL.4 | 200 nm | Minimum width of nwell/pwell                          |

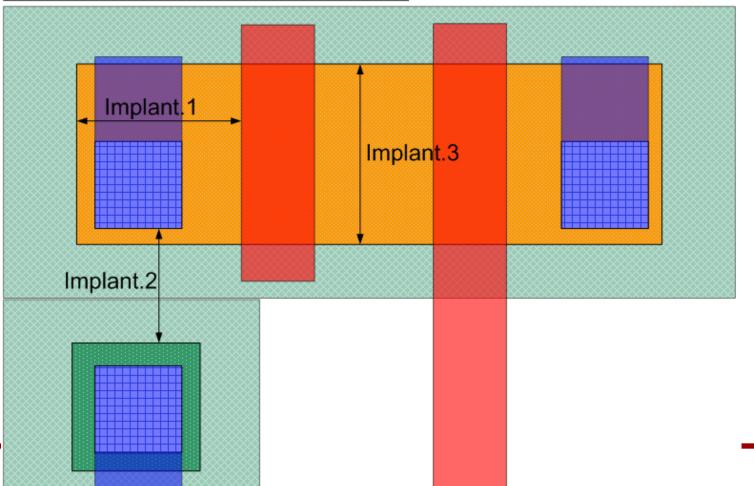

#### FreePDK45:ImplantRules

| Rule        | Value | Description                                      |

|-------------|-------|--------------------------------------------------|

| IMPLANT.1   | 70 nm | Minimum spacing of nimplant/ pimplant to channel |

| IMPLANT.2   | 25 nm | Minimum spacing of nimplant/ pimplant to contact |

| IMPLANT.3/4 | 45 nm | Minimum width/ spacing of nimplant/ pimplant     |

| IMPLANT.5   | none  | Nimplant and pimplant must not overlap           |

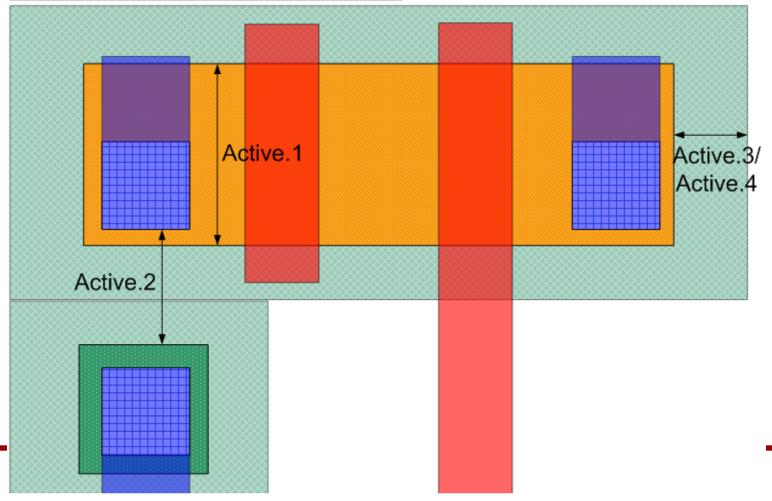

#### FreePDK45:ActiveRules

| Rule     | Value | Description                                        |

|----------|-------|----------------------------------------------------|

| ACTIVE.1 | 90 nm | Minimum width of active                            |

| ACTIVE.2 | 80 nm | Minimum spacing of active                          |

| ACTIVE.3 | 55 nm | Minimum enclosure/spacing of nwell/pwell to active |

| ACTIVE.4 | none  | saveDerived: active must be inside nwell or pwell  |

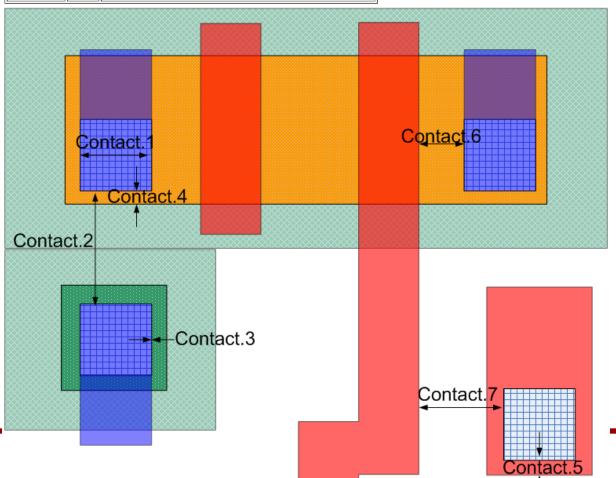

#### FreePDK45:ContactRules

| Rule      | Value | Description                                                  |

|-----------|-------|--------------------------------------------------------------|

| CONTACT.1 | 65 nm | Minimum width of contact                                     |

| CONTACT.2 | 75 nm | Minimum spacing of contact                                   |

| CONTACT.3 | none  | saveDerived: contact must be inside active or poly or metal1 |

| CONTACT.4 | 5 nm  | Minimum enclosure of active around contact                   |

| CONTACT.5 | 5 nm  | Minimum enclosure of poly around contact                     |

| CONTACT.6 | 35 nm | Minimum spacing of contact and gate                          |

| CONTACT.7 | 90 nm | Minimum spacing of contact and poly                          |

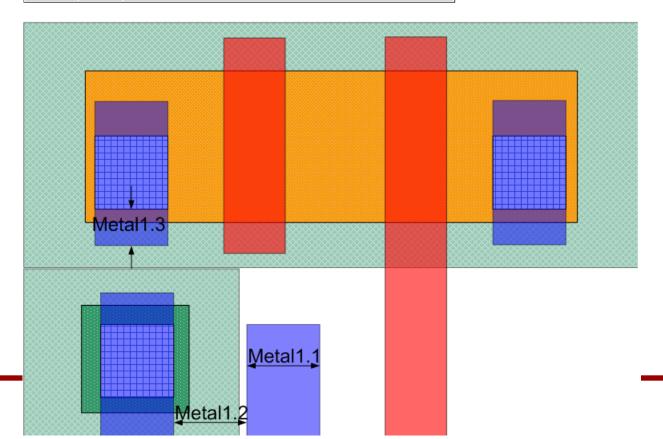

#### FreePDK45:Metal1Rules

| Rule     | Value   | Description                                                        |

|----------|---------|--------------------------------------------------------------------|

| METAL1.1 | 65 nm   | Minimum width of metal1                                            |

| METAL1.2 | 65 nm   | Minimum spacing of metal1                                          |

| METAL1.3 | 35 nm   | Minimum enclosure around contact on two opposite sides             |

| METAL1.4 | 35 nm   | Minimum enclosure around via1 on two opposite sides                |

| METAL1.5 | 90 nm   | Minimum spacing of metal wider than 90 nm and longer than 900 nm   |

| METAL1.6 | 270 nm  | Minimum spacing of metal wider than 270 nm and longer than 300 nm  |

| METAL1.7 | 500 nm  | Minimum spacing of metal wider than 500 nm and longer than 1.8um   |

| METAL1.8 | 900 nm  | Minimum spacing of metal wider than 900 nm and longer than 2.7 um  |

| METAL1.9 | 1500 nm | Minimum spacing of metal wider than 1500 nm and longer than 4.0 um |

#### FreePDK45:Via1Rules

| Rule   | Value | Description                             |

|--------|-------|-----------------------------------------|

| VIA1.1 | 65 nm | Minimum width of via1                   |

| VIA1.2 | 75 nm | Minimum spacing of via1                 |

| VIA1.3 | none  | saveDerived: via1 must be inside metal1 |

| VIA1.4 | none  | saveDerived: via1 must be inside metal2 |

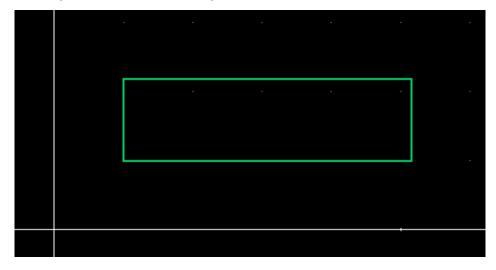

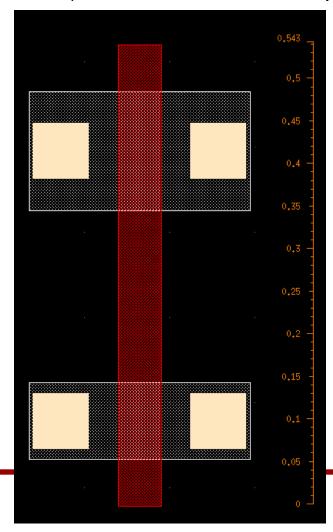

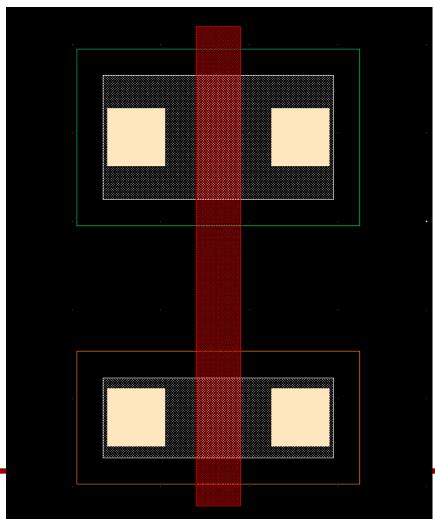

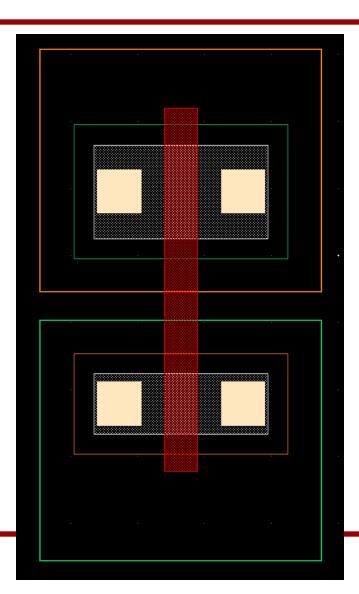

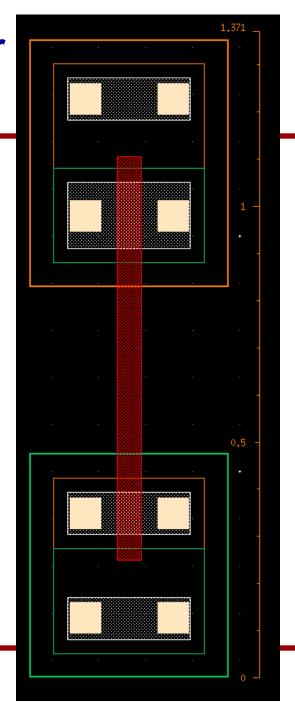

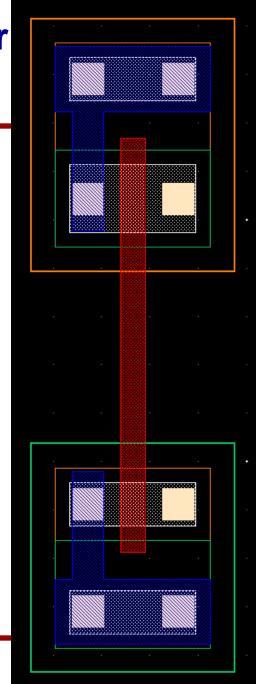

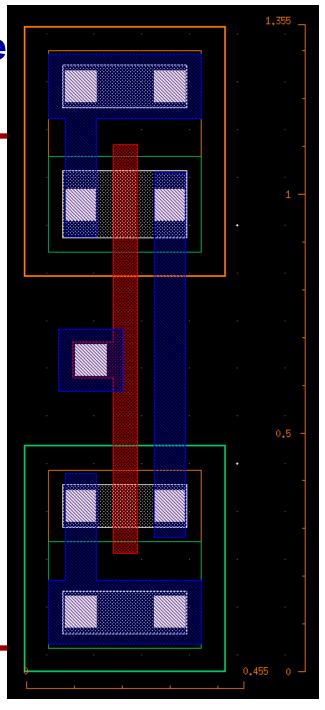

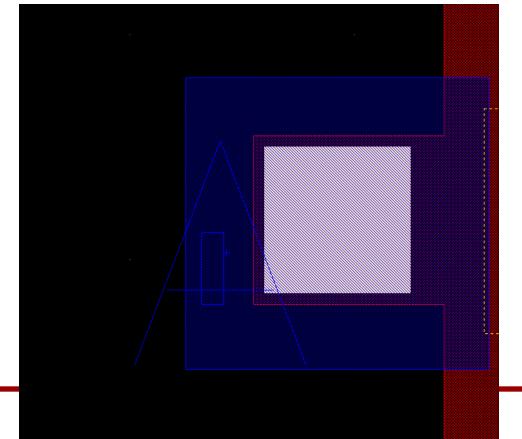

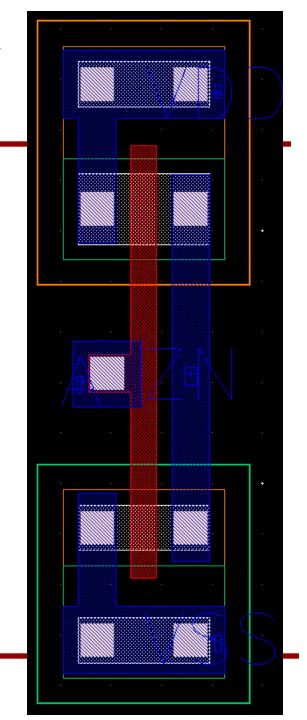

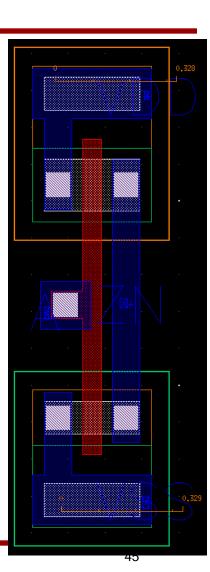

1. poly, active, and contact (Ln=50nm, Wn=90nm, Lp=50nm, Wp=140nm).

2. pimplant and nimplant.

3. pwell and nwell

4. body contacts.

5. VDD and VSS.

6. Input and output.

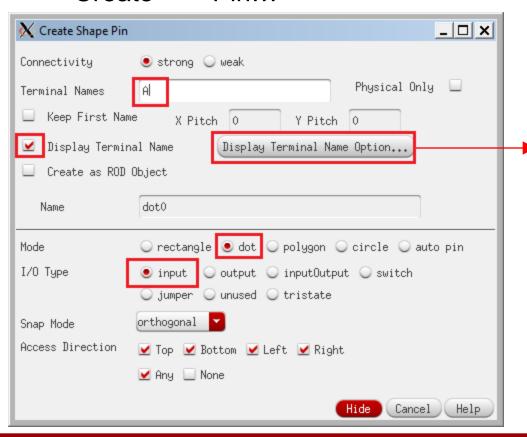

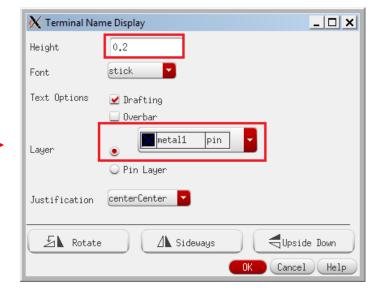

- 7. Create pins (A, ZN, VDD, VSS).

- "Create" → "Pin..."

7. Create pins (A, ZN, VDD, VSS).

- Then, create a small rectangle inside the target pin.

- Make sure that the + mark of the pin is placed inside the wire

object.

- 7. Create pins (A, ZN, VDD, VSS).

- A: input

- ZN: output

- VDD, VSS: inputOutput

- 8. Save the design.

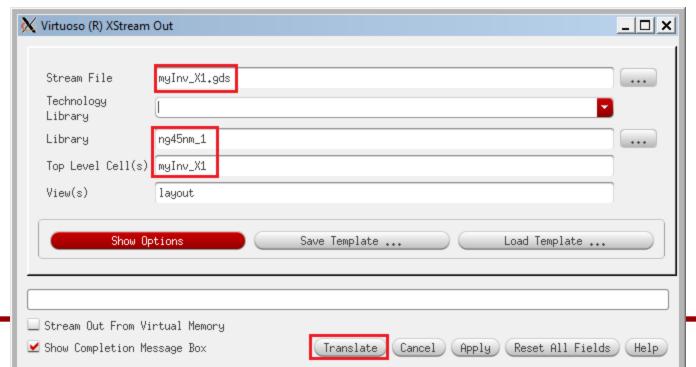

- 9. Export the design into gdsii.

- In CIW, click "File" → "Export" → "Stream...".

- Click "Translate".

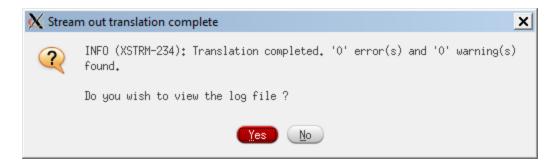

#### 10. Export

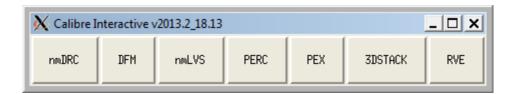

- 1. Let's run DRC.

- 2. Source calibre.sh.

- > source sh/calibre.sh

- 3. Run Calibre.

- > calibre -gui

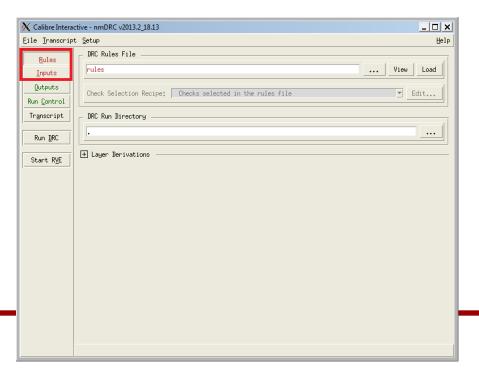

- 4. Click "nmDRC".

- 5. Close the "Load Runset File" window.

- 6. The red texts mean that some files in the input tabs are missing.

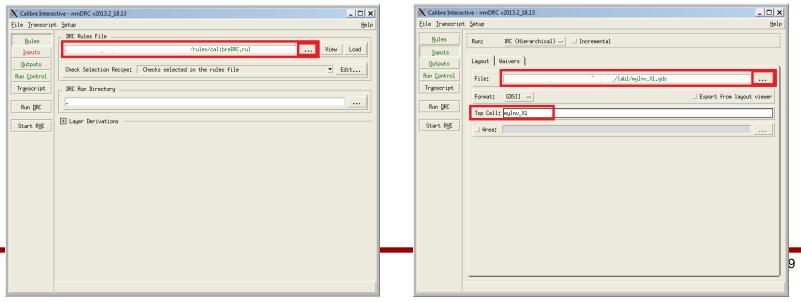

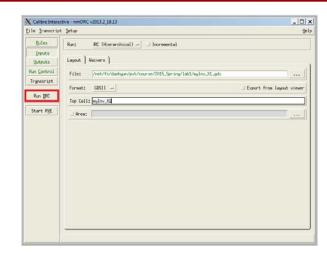

- 7. Click "Rules", and "..." in the "DRC Rules File" and choose "rules/calibreDRC.rul".

- 8. Click "Inputs" and "..." in the "File" and choose the gdsii file you exported.

- 9. Enter the name of your inverter cell.

- 10. Click "Run DRC" to run Calibre DRC.

- 11. It will show two windows.

- DRC Summary Report

- Calibre RVE

- 12. Close the Summary Report window.

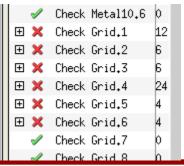

- 13. See the RVE window. I have the following errors.

14. Ignore the "Check Grid.#" errors.

15. If you have any errors, fix them in the layout window (Virtuoso), re-export, and run DRC again.

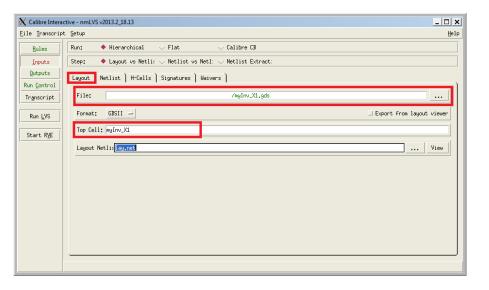

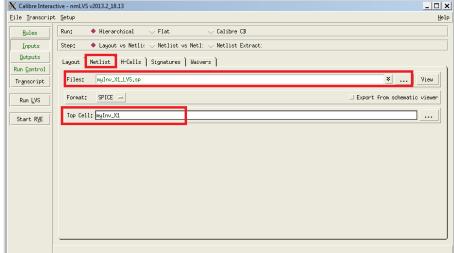

- 1. Let's run LVS.

- 2. Click "nmLVS" in the main Calibre window.

- 3. Close the "Load Runset File" window.

- 4. Select the "calibreLVS.rul" in the LVS rule file section.

5. Click "Inputs". We need to enter the name of the file containing the layout and the netlist file.

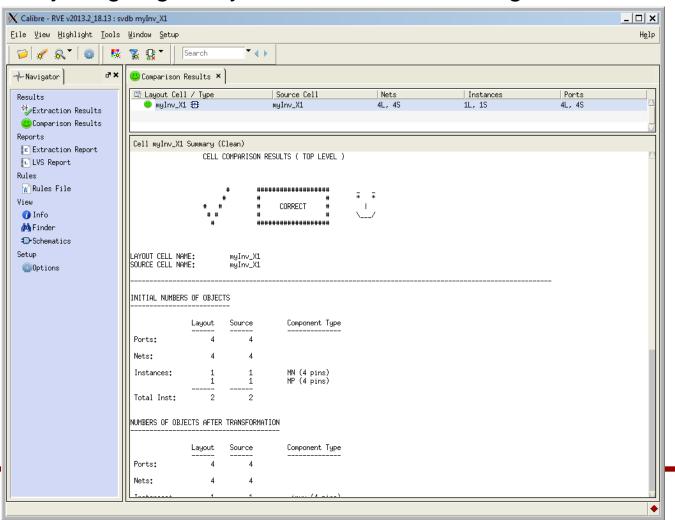

6. If everything is good, you will see the following window:

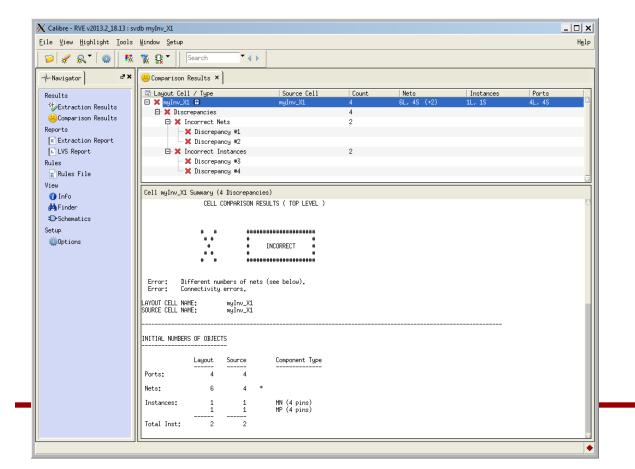

7. I'll remove the body contacts and see what happens.

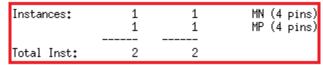

8. First of all, match "Ports", which are primary inputs and outputs.

9. Then, match "Instances".

10. Then, match "Nets".

- In the source (the SPICE netlist), there are four nets, which makes sense (A, ZN, VDD, VSS).

- In the layout, however, there are six nets, so something is wrong in the layout.

11. Click "Discrepancy #".

- It says that the body (substrate) of M1 (the PMOS transistor) in the layout is connected to net "6", but that in the source is connected to "VDD".

- From this, we know that the body of M1 is NOT connected VDD.

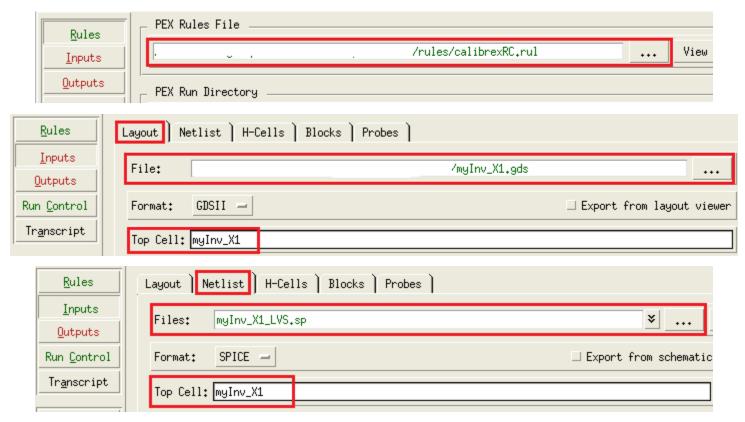

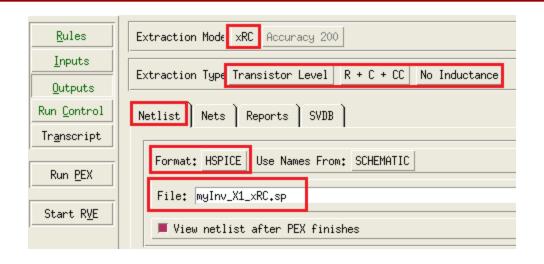

- 1. Let's run xRC.

- 2. Click "PEX" in the Calibre main window.

3. Click "Run PEX".

4. xRC netlist (myInv\_X1\_xRC.sp)

```

* File: myInv_X1_xRC.sp

* Created: Mon Feb 16 13:29:12 2015

* Program "Calibre xRC"

* Version "v2013.2_18.13"

* .include "myInv_X1_xRC.sp.pex"

.subckt myInv_X1 A VSS VDD ZN

* ZN ZN

* VDD VDD

* VSS VSS

* A A

mnl N_ZN_mnl_d N_A_mnl_g N_VSS_mnl_s N_VSS_mnl_b NMOS_HP L=5e-08 W=9e-05

# AD=9.45e-15 AS=9.45e-15 PD=8.9e-07 PS=8.9e-07

mpl N_ZN_mpl_d N_A_mpl_g N_VDD_mpl_s N_VDD_mpl_b PMOS_HP L=5e-08 W=1.4e-07

# AD=1.47e-14 AS=1.47e-14 PD=4.9e-07 PS=4.9e-07

* .include "myInv_X1_xRC.sp.MYINV_X1.pxi"

* .ends

```

### **Example – Inverter SPICE Simulation**

- 1. Let's run HSPICE for the inverter.

- > hspice myInv\_X1\_simul.sp

- > hspice myInv\_X1\_noRC\_simul.sp

- 2. The following shows my result:

|                   | Fall     | Rise     |

|-------------------|----------|----------|

| Without RC        | 112.67ps | 123.11ps |

| With parasitic RC | 119.29ps | 132.62ps |

| Difference        | +6.62ps  | +9.51ps  |