## Homework Assignment 3 (Due Feb. 10th at the beginning of the class)

\* Submission policy: Please zip all your result files into a single file and send it to <a href="mailto:daehyun@eecs.wsu.edu">daehyun@eecs.wsu.edu</a>. The file name should be <a href="mailto:lastname\_firststname.zip">lastname\_firststname.zip</a> (or .tar.gz or .tar ...)

Go to the course website, click "Labs", and open "tutorial-design\_compiler.pdf" and complete it (but you don't need to submit anything for the tutorial).

- (1) [Library Analysis, 10 points] Open ng45.lib in a text editor. This is the Nangate 45nm standard cell timing/power library.

- Find cell INV\_X1. It has all the information about the smallest inverter cell (X1 is the size). Most of the lines in the file are self-explanatory.

- [Submit] The area of the INV\_X1 cell. (the area unit is um<sup>2</sup>).

- $\circ$  0.532 um<sup>2</sup>

- [Submit] Find the output pin (ZN) of INV\_X1. What is the function of the output pin?

- o !A (NOT A)

- Find cell FA X1. This is a full-adder cell.

- [Submit] The area of the FA\_X1 cell.

- o 4.256 um<sup>2</sup>

- [Submit] Find the carry-out pin (CO) of FA\_X1. What is the function of the output pin? (Express the function as a function of the input pins A, B, CI and the Boolean operations, (AND) and + (OR).)

- $\circ$  ((A & B) | (CI & (A | B))) = A•B+CI•(A+B)

- Find cell DFF\_X1. This is a D F/F cell.

- [Submit] The area of the DFF\_X1 cell.

- o 4.522 um<sup>2</sup>

- [Submit] The "cell\_leakage\_power" of the DFF\_X1 cell. The unit is nW.

- o 79.112308 nW

- (2) [Synthesis, 20 points] Download the following file into your working directory.

- http://eecs.wsu.edu/~ee434/Homework/hw03.zip

- Unzip it.

- Synthesize hw03\_and6.v using the default compile command (compile exact\_map). It implements a six-input AND gate.

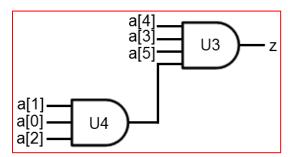

- [Submit] A gate-level schematic of the synthesized netlist.

- [Submit] Total area (run "report\_area" to get the total area).

- o 2.926 um<sup>2</sup>

- Copy hw03\_and6.v into hw03\_and20.v.

- o cp hw03\_and6.v hw03\_and20.v

- We are going to make a 20-input AND gate. Modify hw03\_and20.v in a text editor.

- o Change the module name from Vand6 to Vand20.

- o Change the input pin from [5:0] a to [19:0] a.

- o Change the assign statement to implement a 20-input AND gate.

- Synthesize it (compile –exact\_map).

- [Submit] Total area.

- $\circ$  10.906 um<sup>2</sup>

- [Submit] Total dynamic power consumption (use "report\_power").

- o 1.8571 uW

## (3) [Synthesis, 10 points] Timing optimization

- Create a 40-input AND gate.

- Synthesize it (compile –exact\_map).

- [Submit] Total area and total dynamic power consumption.

- o 21.812 um<sup>2</sup>

## o 3.8561 uW

- Run the following command to set up a timing constraint (160ps from any input to the output).

- o set\_max\_delay –from  $\{a^*\}$  –to  $\{z\}$  0.16

- Synthesize the design again, but add the following options.

- o compile -exact\_map -map\_effort high

- [Submit] Total area and total dynamic power consumption.

- o 24.738 um<sup>2</sup>

- o 4.3845 uW

- Run "report\_timing" to get timing info.

- [Submit] Slack (the last line in the timing report).

- o 0.01 ns