# EE434 ASIC & Digital Systems

# Automatic Layout Generation (Encounter)

Spring 2017

Dae Hyun Kim

daehyun@eecs.wsu.edu

### **Preparation for Lab3**

- Download the following file into your working directory.

- wget http://eecs.wsu.edu/~ee434/Labs/lab3.tar.gz

- Unzip it.

- tar xvfz lab3.tar.gz

## What We Are Going To Do

- 1. Chip outlining

- 2. P/G network design

- Placement

- 4. Pre-CTS optimization

- 5. CTS

- 6. Post-CTS optimization

- 7. Routing

- 8. Post-routing optimization

- 9. Fill insertion

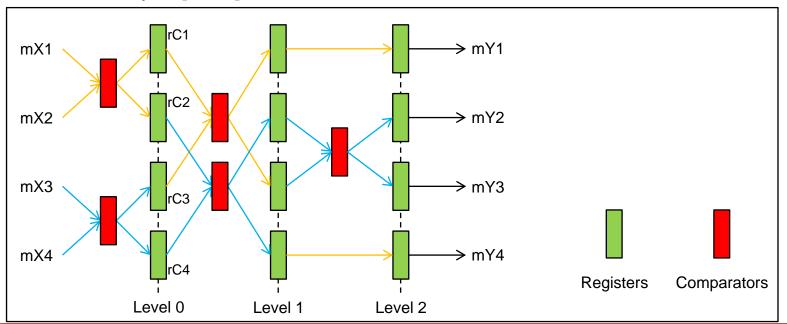

#### Benchmark

- VQS64\_4 (four-input 64-bit pipelined quick sort)

- input [63:0] mX1, mX2, mX3, mX4

- input mCLK

- output [63:0] mY1, mY2, mY3, mY4

- VQS64\_4\_fm.globals

- init\_pwr\_net: Power nets.

- init\_gnd\_net: Ground nets.

- init\_lef\_file: Physical library files.

- init\_mmmc\_file: Analysis view files.

- mmmc: Multi-mode multi-corner

- init\_verilog: Verilog netlists.

- VQS64\_4\_fm.view

- create\_rc\_corner: Capacitance table + RC analysis corner

- create\_library\_set: Library files

- create\_constraint\_mode: Constraint files

- create\_delay\_corner: Library + RC corner

- create\_analysis\_view: Analysis view

- set\_analysis\_view: Setup and hold analysis view

- Source "edi.sh".

- % source edi.sh

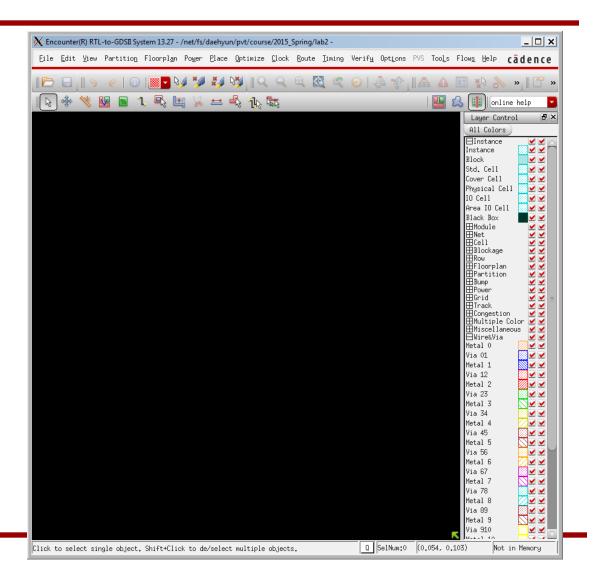

- Run Encounter.

- % encounter

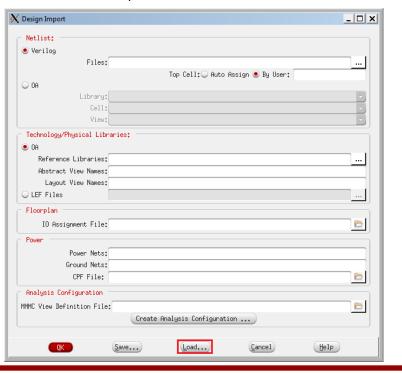

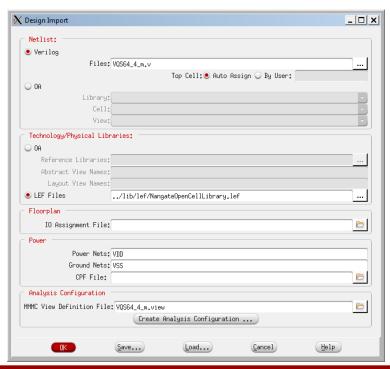

- Click "File" → "Import Design…".

- In the "Design Import" window, click "Load..." and choose "VQS64\_4\_m.globals". This will automatically fill up the settings. Then, click "OK".

- See the terminal for Encounter messages. There might be some Error or Warning messages.

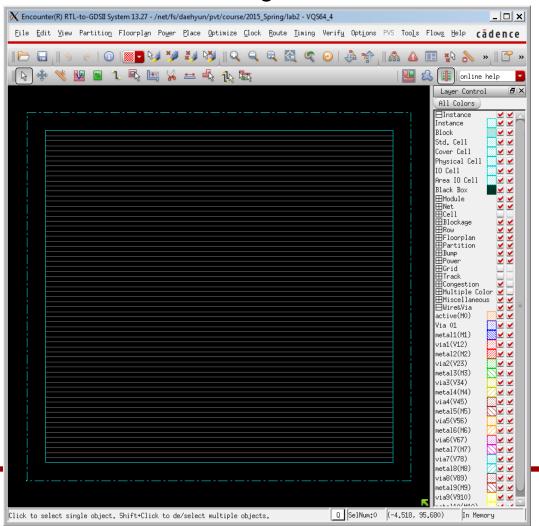

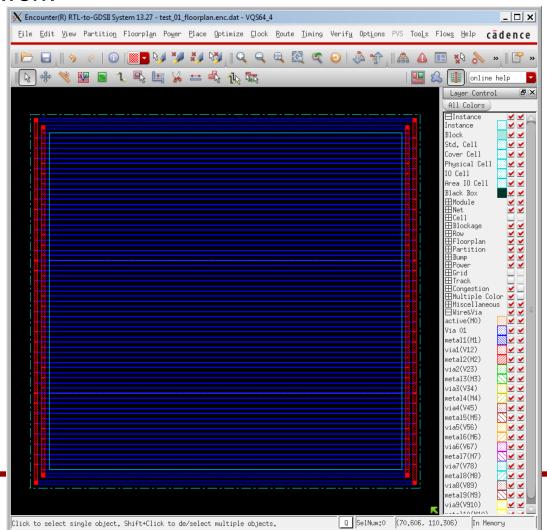

- In the Encounter main window, press "f" to see the outline of the layout.

- Encounter automatically computes and prepares the layout area.

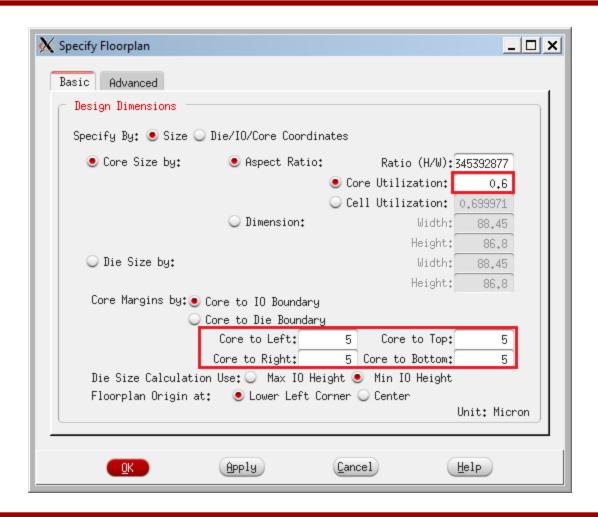

- In the main window, click "Floorplan" → "Specify Floorplan...".

- Set the core utilization to 0.6.

- Set the core-to-left, core-to-top, core-to-right, and core-to-bottom to 5.0.

- Then, click OK.

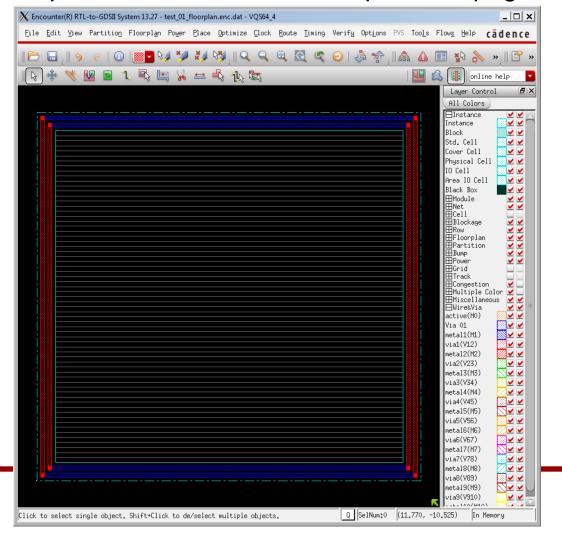

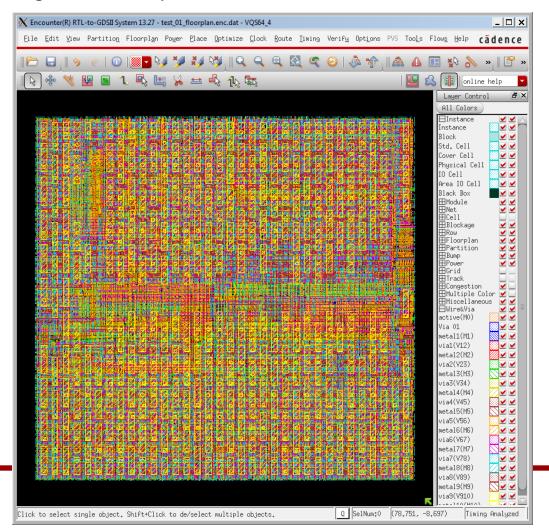

Now, you will see the following window.

#### Save

- Let's save the current design.

- In the terminal, run the following command to save the current design into "test\_01\_floorplan.enc".

- encounter #> saveDesign test\_01\_floorplan.enc

- Later on, you can load the design as follows.

- When you launch Encounter, add the following option to load the specified design.

- encounter –init test\_01\_floorplan.enc

- or, after you launch Encounter, run the following command.

- source test\_01\_floorplan.enc

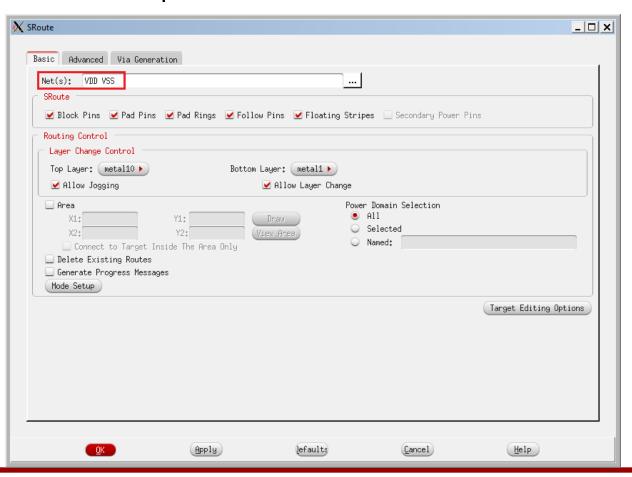

Click "Power" → "Power Planning" → "Add Rings…".

Fill in the input boxes as shown in the previous page and click

OK.

Click "Route" → "Special Route…".

#### P/G network

saveDesign test\_02\_pg.enc

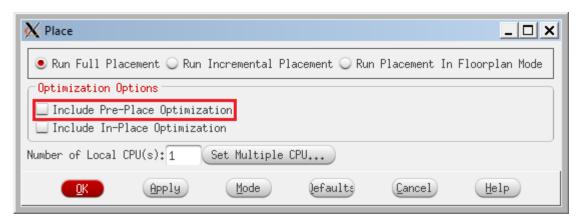

#### 3. Placement

- Let's place the instances (cells).

- In the main window, click "Place" → "Place Standard Cell".

- In the following window, turn off "Include Pre-Place Optimization".

Then, click "OK" to run Placement.

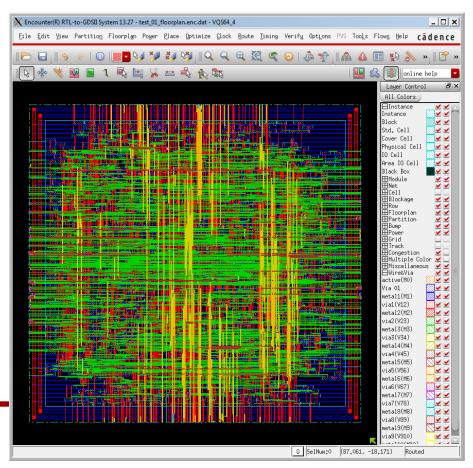

#### 3. Placement

- It shows placement and trialRoute results.

- See the terminal. It shows some more information.

- Total wire length: 46,920um

- Save it.

- saveDesign test\_03\_pl.enc

```

Total length: 4.692e+04um, number of vias: 17032 M1(H) length: 1.187e+03um, number of vias: 9371 M2(V) length: 2.059e+04um, number of vias: 6881 M3(H) length: 1.976e+04um, number of vias: 506 M4(V) length: 3.390e+03um, number of vias: 167 M5(H) length: 1.261e+03um, number of vias: 68 M6(V) length: 7.066e+02um, number of vias: 25 M7(H) length: 9.350e+00um, number of vias: 8 M8(V) length: 6.480e+00um, number of vias: 6 M9(H) length: 4.140e+00um, number of vias: 0 M10(V) length: 0.000e+00um

```

## **Visibility**

Let's see the placement result only.

Turn off the following check-box to turn off the visibility of the

wires.

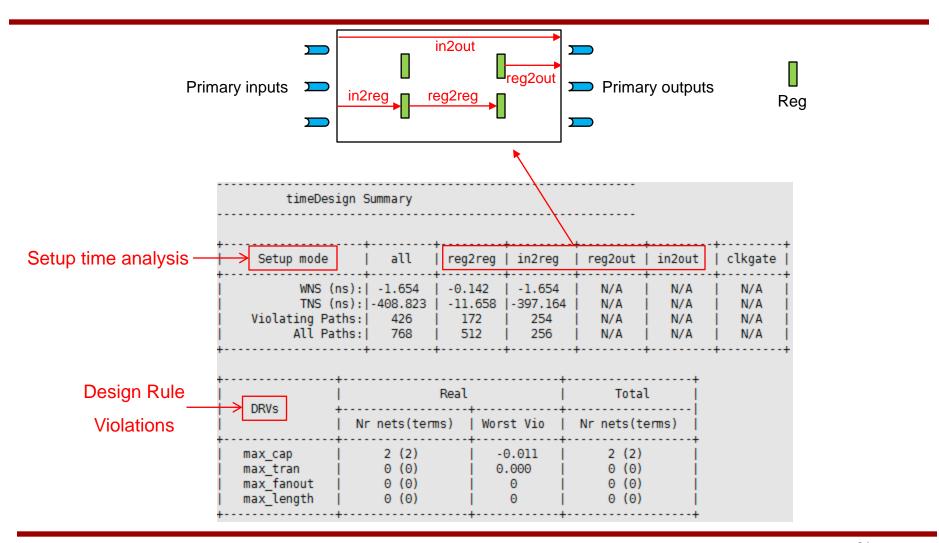

- Run the following command to turn off SI-awareness.

- encounter #> setDelayCalMode -siAware false

- Then, run the following command to analyze setup time.

- encounter #> timeDesign –preCTS

- It will show the following summary:

- Run the following command to check the longest path.

- encounter #> report\_timing

| Path 1: VIOLATED So<br>Endpoint: rCl_red<br>Beginpoint: mX2[1]<br>Analysis View: NG_Y<br>Other End Arrival<br>- Setup<br>+ Phase Shift<br>= Required Time<br>- Arrival Time<br>= Slack Time<br>Clock Rise Edu<br>+ Input Delay<br>= Beginpoint | g[52]/D (v) check<br>(^) trigoview_typ<br>Time 0.00.00.00.00.00.00.00.00.00.00.00.00.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ked with le<br>gered by le<br>000<br>047<br>000<br>953<br>606                                                                                                                                                                                                                                                                                                                  | ading ed<br>ading ed<br>0<br>0                                                                                                            |                                                                                        | .K'                                                                            |   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|---|

| Instance                                                                                                                                                                                                                                       | Arc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Cell                                                                                                                                                                                                                                                                                                                                                                           | Delay                                                                                                                                     | Arrival<br>  Time                                                                      | Required  <br>  Time                                                           |   |

| U4103<br>  U3853<br>  U3852<br>  U3861<br>  U3860<br>  U3859<br>  U3858<br>  U3869<br>  U3866<br>  U3867<br>  U3866<br>  U3877<br>  U3876<br>  U3875<br>  U3874<br>  U3885<br>  U3884<br>  U3884<br>  U3883                                    | mX2[1] ^   A ^ -> ZN v   C2 v -> ZN ^   A ^ -> ZN v   A V -> ZN ^ -> ZN ^ -> ZN ^ -> ZN v   A V -> ZN ^ -> Z | INV_X1<br>  OAI211_X1<br>  OAI221_X1<br>  OAI221_X1 | 0.026<br>  0.041<br>  0.028<br>  0.040<br>  0.027<br>  0.040<br>  0.029<br>  0.041<br>  0.028<br>  0.041<br>  0.028<br>  0.041<br>  0.028 | 0.105<br>0.146<br>0.174<br>0.214<br>0.241<br>0.281<br>0.311<br>0.352<br>0.380<br>0.421 | -1.643  <br>-1.609  <br>-1.575  <br>-1.549  <br>-1.508  <br>-1.480  <br>-1.440 | _ |

|   | U3946       | A ^ -> ZN v  | OAI221_X1 | 0.039 | 1.707 | 0.053 |

|---|-------------|--------------|-----------|-------|-------|-------|

|   | U3957       | A v -> ZN ^  | 0AI221_X1 | 0.027 | 1.734 | 0.080 |

|   | U3956       | A ^ -> ZN v  | 0AI221_X1 | 0.040 | 1.774 | 0.120 |

|   | U3955       | A v -> ZN ^  | OAI221_X1 | 0.029 | 1.803 | 0.149 |

|   | U3954       | A ^ -> ZN v  | OAI221_X1 | 0.041 | 1.843 | 0.190 |

|   | U3965       | A v -> ZN ^  | OAI221_X1 | 0.028 | 1.872 | 0.218 |

|   | U3964       | A ^ -> ZN v  | OAI221_X1 | 0.042 | 1.914 | 0.260 |

|   | U3963       | A v -> ZN ^  | OAI221_X1 | 0.029 | 1.943 | 0.289 |

|   | U3962       | A ^ -> ZN v  | OAI221_X1 | 0.042 | 1.985 | 0.331 |

|   | U3973       | A v -> ZN ^  | OAI221_X1 | 0.027 | 2.011 | 0.358 |

|   | U3972       | A ^ -> ZN v  | OAI221_X1 | 0.040 | 2.051 | 0.397 |

|   | U3971       | A v -> ZN ^  | OAI221_X1 | 0.026 | 2.077 | 0.424 |

|   | U3970       | A ^ -> ZN v  | 0AI21_X1  | 0.024 | 2.102 | 0.448 |

|   | U4233       | A v -> ZN ^  | 0AI21_X1  | 0.021 | 2.123 | 0.469 |

|   | U4232       | A ^ -> ZN v  | 0AI221_X1 | 0.034 | 2.157 | 0.503 |

|   | U4231       | A v -> ZN ^  | 0AI21_X1  | 0.113 | 2.270 | 0.616 |

|   | U3648       | A ^ -> ZN v  | INV_X1    | 0.025 | 2.295 | 0.642 |

|   | U3330       | A v -> Z v   | BUF_X1    | 0.050 | 2.346 | 0.692 |

|   | U3273       | A v -> Z v   | BUF_X1    | 0.055 | 2.401 | 0.747 |

|   | U3255       | A v -> ZN ^  | INV_X1    | 0.157 | 2.557 | 0.903 |

|   | U3513       | B2 ^ -> ZN v | 0AI22_X1  | 0.049 | 2.606 | 0.953 |

|   | rCl_reg[52] | D v          | DFF_X1    | 0.000 | 2.606 | 0.953 |

| - | +           |              |           |       |       | +     |

|   |             |              |           |       |       |       |

## 4. Pre-CTS Optimization

- Run the following command to optimize the design before CTS.

- encounter #> optDesign –preCTS

- (This will take some time, up to 20~30 minutes depending on the machine you are working in).

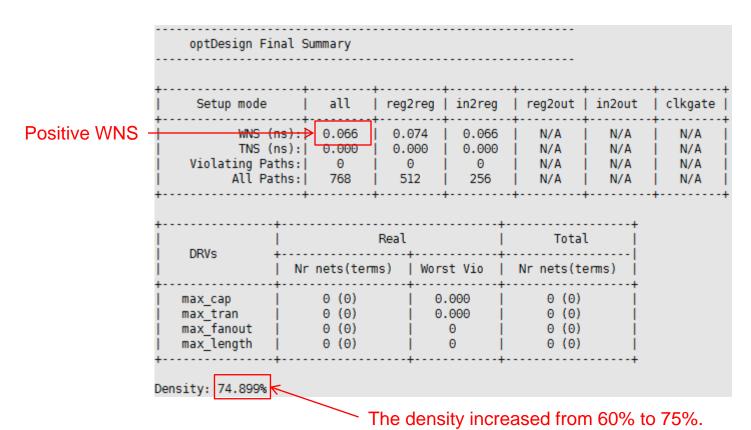

- After Pre-CTS optimization is done, you will see the following result:

#### 4. Pre-CTS Optimization

#### Pre-CTS optimization

# 4. Pre-CTS Optimization

saveDesign test\_04\_prectsopt.enc

- Open "VQS64\_4\_fm.ctstch" in a text editor and see the spec.

- Run the following command to run CTS.

- encounter #> clockDesign –specFile VQS64\_4\_fm.ctstch outDir clk\_report

#### CTS

```

# Analysis View: NG view typ

******* Clock mCLK Post-CTS Timing Analysis ********

Nr. of Subtrees

Nr. of Sinks

: 37←

# buffers inserted

Nr. of Buffer

Nr. of Level (including gates) : 2 ←

# levels

Root Rise Input Tran

: 100(ps)

Root Fall Input Tran

: 100(ps)

No Driving Cell Specified!

Max trig. edge delay at sink(R): rC2 reg[53]/CK 163.3(ps)

Min trig. edge delay at sink(R): mY2 reg[34]/CK 155.5(ps)

(Actual)

(Required)

Rise Phase Delav

: 155.5~163.3(ps)

0~1000(ps)

Fall Phase Delay

: 168.2~175.6(ps)

0~1000(ps)

Trig. Edge Skew

: 7.8(ps)

20(ps)

: 7.8(ps)

Rise Skew

Clock skew

Fall Skew

: 7.4(ps)

Max. Rise Buffer Tran.

: 49.7(ps)

100(ps)

Max. Fall Buffer Tran.

: 44.8(ps)

100(ps)

Max. Rise Sink Tran.

: 29.4(ps)

50(ps)

Max. Fall Sink Tran.

: 29.2(ps)

50(ps)

Min. Rise Buffer Tran.

: 49.7(ps)

0(ps)

Min. Fall Buffer Tran.

: 44.8(ps)

0(ps)

Min. Rise Sink Tran.

: 23.6(ps)

0(ps)

Min. Fall Sink Tran.

: 23.5(ps)

0(ps)

view NG view typ : skew = 7.8ps (required = 20ps)

```

- You can see the clock tree by the following command:

- encounter #> displayClockTree -clk mCLK -level 1

saveDesign test\_05\_cts.enc

- Run the following command to check timing.

- timeDesign –postCTS

| timeDesi                                              | ign S        | Gummary                          |              |                 |                              |                                | -                              |                    |            |

|-------------------------------------------------------|--------------|----------------------------------|--------------|-----------------|------------------------------|--------------------------------|--------------------------------|--------------------|------------|

| Setup mode                                            |              | all                              | +<br>  reg2  | reg             | in2reg                       | reg2ou                         | +<br>t   in2out                | clkg               | +<br>ate   |

| WNS (r<br>  TNS (r<br>  Violating Pat<br>  All Pat    | s): <br>:hs: | 0.000<br>0                       | 0.6<br>  0.6 | 971<br>900<br>9 | 0.207<br>0.000<br>0<br>256   | N/A<br>  N/A<br>  N/A<br>  N/A | N/A<br>  N/A<br>  N/A<br>  N/A | N/<br>  N/<br>  N/ | A İ<br>A İ |

| DRVs +                                                |              |                                  | Real         |                 | <br>                         | To                             | +<br>tal                       |                    |            |

|                                                       | Nr           | nets(ten                         | ns)          | Wors            | st Vio                       | Nr nets                        | (terms)                        |                    |            |

| max_cap<br>  max_tran<br>  max_fanout<br>  max_length |              | 0 (0)<br>0 (0)<br>0 (0)<br>0 (0) |              |                 | .000  <br>.000  <br>0  <br>0 | 0 (1<br>0 (1<br>0 (1           | 9) j                           |                    |            |

| Density: 75.449%                                      |              |                                  |              |                 |                              |                                |                                |                    |            |

#### 6. Post-CTS Optimization

- Although we already satisfied the timing without any further optimization after CTS, we will run post-CTS optimization.

- encounter #> optDesign –postCTS

| optDesign Fir                                   | nal S         | ummary                           |                                |                 |                            |      |                                  |                                |   |                          |

|-------------------------------------------------|---------------|----------------------------------|--------------------------------|-----------------|----------------------------|------|----------------------------------|--------------------------------|---|--------------------------|

| Setup mode                                      |               | all                              | reg2                           | 2reg            | in2reg                     | reg  | 2out                             | +<br>  in2out                  | + | clkgate                  |

| WNS (r<br>TNS (r<br>Violating Pat<br>All Pat    | ns): <br>ths: |                                  | 0.6                            | 121<br>900<br>9 | 0.101<br>0.000<br>0<br>256 | N,   | /A<br>/A<br>/A<br>/A             | N/A<br>  N/A<br>  N/A<br>  N/A |   | N/A<br>N/A<br>N/A<br>N/A |

| DRVs -                                          | Nr            | nets(tem                         | Real<br>ets(terms)   Worst Vio |                 |                            | Nr n | Tota<br>Tota<br><br>ets(t        | i                              |   |                          |

| max_cap<br>max_tran<br>max_fanout<br>max_length |               | 0 (0)<br>0 (0)<br>0 (0)<br>0 (0) |                                | 0               | .000  <br>.000  <br>0      | (    | 0 (0)<br>0 (0)<br>0 (0)<br>0 (0) |                                |   |                          |

| nsity: 65.532%                                  |               |                                  |                                | +               | +                          |      |                                  | +                              |   |                          |

# **6. Post-CTS Optimization**

saveDesign test\_06\_postctsopt.enc

- Run the following command to check timing.

- timeDesign –postCTS

| timeDesi                                              | ign Summary                      |                |                 |                                  |                                |                                |                                |

|-------------------------------------------------------|----------------------------------|----------------|-----------------|----------------------------------|--------------------------------|--------------------------------|--------------------------------|

| Setup mode                                            | all                              | +<br>  reg2    | 2reg            | in2reg                           | reg2out                        | in2out                         | -+<br>  clkgate                |

| WNS (n<br>TNS (n<br>Violating Pat<br>All Pat          | ns):  0.000<br>ths:  0           | 0.6            | 121<br>900<br>9 | 0.101<br>  0.000<br>  0<br>  256 | N/A<br>  N/A<br>  N/A<br>  N/A | N/A<br>  N/A<br>  N/A<br>  N/A | N/A<br>  N/A<br>  N/A<br>  N/A |

| DDVo                                                  | <del></del>                      | Real           |                 | <u>+</u><br>!                    | Tota                           | l                              |                                |

| DRVs +                                                | Nr nets(ter                      | ms)            | Wors            | st Vio                           | Nr nets(t                      | erms)                          |                                |

| max_cap  <br>max_tran  <br>max_fanout  <br>max_length | 0 (0)<br>0 (0)<br>0 (0)<br>0 (0) | 0 (0)<br>0 (0) |                 | 0.000  <br>  0.000  <br>  0      |                                |                                |                                |

| nsity: 65.532%                                        |                                  |                |                 | +                                |                                | +                              |                                |

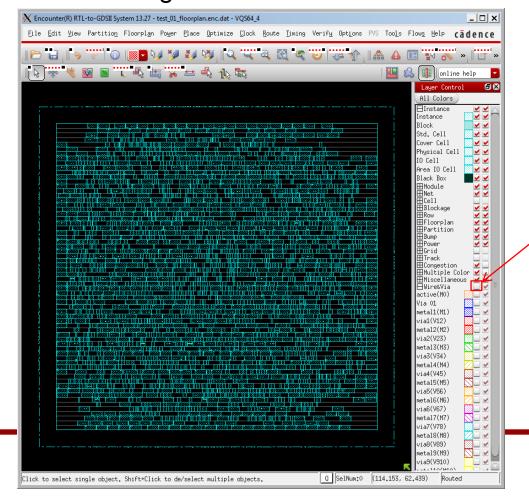

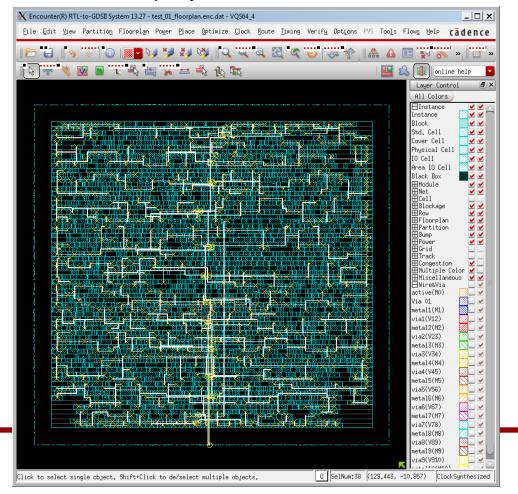

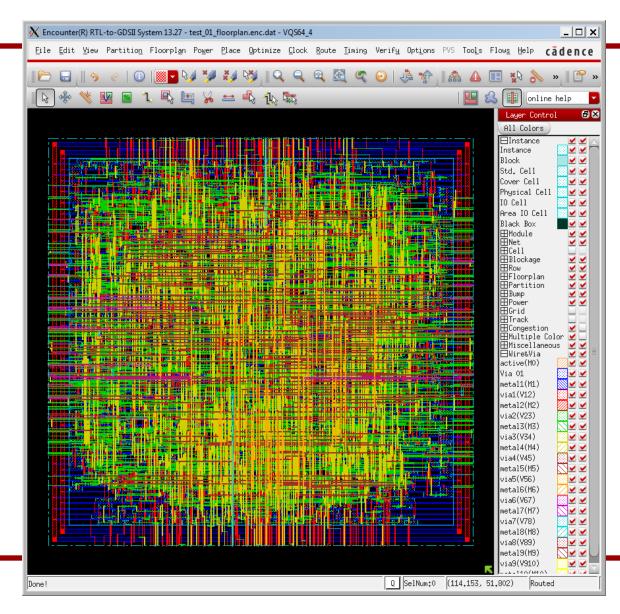

- Click "Route" → "NanoRoute" → "Route...".

- Turn off "Fix Antenna" and click OK to run routing.

• Routing result.

- Routing result.

- Wirelength: 52,077um

- No DRC violations.

```

#Complete Detail Routing.

#Total number of nets with non-default rule or having extra spacing = 38

#Total wire length = 52077 um

#Total half perimeter of net bounding box = 48628 um.

#Total wire length on LAYER metal1 = 1604 um.

#Total wire length on LAYER metal2 = 15448 um.

#Total wire length on LAYER metal3 = 19261 um.

#Total wire length on LAYER metal4 = 9446 um.

#Total wire length on LAYER metal5 = 4644 um.

#Total wire length on LAYER metal6 = 1314 um.

#Total wire length on LAYER metal7 = 236 um.

#Total wire length on LAYER metal8 = 68 um.

#Total wire length on LAYER metal9 = 56 um.

#Total wire length on LAYER metal10 = 0 um.

#Total number of vias = 24082

#Up-Via Summary (total 24082):

Metal 1

10605

Metal 2

10028

Metal 3

2748

Metal 4

515

Metal 5

147

Metal 6

Metal 7

Metal 8

24082

#Total number of DRC violations = 0

```

saveDesign test\_07\_route.enc

- Run the following command to check timing.

- timeDesign –postRoute

| timeDes                                               | ign Su                   | ummary                           |                                        |      |                              |            |                                  |               |   |                                |

|-------------------------------------------------------|--------------------------|----------------------------------|----------------------------------------|------|------------------------------|------------|----------------------------------|---------------|---|--------------------------------|

| + <br>  Setup mode                                    | ·+                       | all                              | <br>  reg2                             | reg  | in2reg                       | -+<br>  re | g2out                            | +<br>  in2out | + | clkgate                        |

| + WNS (r<br>  TNS (r<br>  Violating Pat<br>  All Pat  | ns):  0.000  <br>ths:  0 |                                  | 0.139  <br>  0.000  <br>  0  <br>  512 |      | 0.102<br>  0.000<br>  0      |            |                                  | +             |   | N/A  <br>N/A  <br>N/A  <br>N/A |

| +                                                     |                          |                                  |                                        |      | +                            |            |                                  |               |   | ,                              |

| l DRVs -                                              | <br>                     |                                  | Real                                   |      |                              |            | Tota                             | l             |   |                                |

|                                                       | Nr                       | nets(tem                         | ıs)                                    | Wors | st Vio                       | Nr         | nets(t                           | emns) ¦       |   |                                |

| max_cap<br>  max_tran<br>  max_fanout<br>  max_length |                          | 0 (0)<br>0 (0)<br>0 (0)<br>0 (0) |                                        |      | .000  <br>.000  <br>0  <br>0 |            | 0 (0)<br>0 (0)<br>0 (0)<br>0 (0) |               |   |                                |

| Density: 65.532%                                      |                          |                                  |                                        |      |                              |            |                                  |               |   |                                |

## 8. Post-Routing Optimization

- Although we already satisfied the timing without any further optimization after routing, we will run post-routing optimization.

- encounter #> optDesign –postRoute

| optDesign Fin                                | nal Non-SI 1                     | Timing Su | ımmary |                            |                                  |                          |                                |

|----------------------------------------------|----------------------------------|-----------|--------|----------------------------|----------------------------------|--------------------------|--------------------------------|

| Setup mode                                   | all                              | reg2      | reg    | in2reg                     | reg2out                          | in2out                   | clkgate                        |

| WNS (n<br>TNS (n<br>Violating Pat<br>All Pat | s):  0.000<br>hs:  0             | ) i 0.6   | ) j    | 0.102<br>0.000<br>0<br>256 | N/A<br>  N/A<br>  N/A<br>  N/A   | N/A<br>N/A<br>N/A<br>N/A | N/A<br>  N/A<br>  N/A<br>  N/A |

| DRVs +                                       | Nr nets(t                        | Real      | Worst  | +-<br> <br>+-<br>t Vio     | Total                            | ·i                       |                                |

| max_cap  <br>max_tran  <br>max_fanout        | 0 (0)<br>0 (0)<br>0 (0)<br>0 (0) |           | 0.0    | 900  <br>900  <br>9        | 0 (0)<br>0 (0)<br>0 (0)<br>0 (0) |                          |                                |

# 8. Post-Routing Optimization

saveDesign test\_08\_postrouteopt.enc

#### 9. Fill Insertion

- Click "Route" → "Metal Fill" → "Setup…".

- Click "Load" and choose "metalfill.cmd" to load the setting I made.

- Click OK.

- Click "Route" → "Metal Fill" → "Add".

- Click OK to insert metal fills.

#### 9. Fill Insertion

The following shows my fill insertion result.

- Run the following command to analyze timing.

- encounter #> timeDesign –postRoute

| timeDesi                                              | gn Sum        | mary                             |              |                 |                            |                |                                  |                                |   |                          |

|-------------------------------------------------------|---------------|----------------------------------|--------------|-----------------|----------------------------|----------------|----------------------------------|--------------------------------|---|--------------------------|

| Setup mode                                            |               | all                              | +<br>  reg2  | 2reg            | <br>  in2reg               | +<br>  r       | eg2out                           | +<br>  in2out                  | : | clkgate                  |

| WNS (n<br>TNS (n<br>Violating Pat<br>All Pat          | ns): <br>:hs: | 0.102<br>0.000<br>0<br>768       | 0.6<br>  0.6 | 139<br>000<br>0 | 0.102<br>0.000<br>0<br>256 |                | N/A<br>N/A<br>N/A<br>N/A         | N/A<br>  N/A<br>  N/A<br>  N/A | į | N/A<br>N/A<br>N/A<br>N/A |

|                                                       |               |                                  | Real         |                 |                            | +<br>          | Tota                             | ı                              | + |                          |

| DRVs +                                                | Nr n          | ets(ten                          | ns)          | s)   Worst Vio  |                            | Nr nets(terms) |                                  |                                |   |                          |

| max_cap  <br>max_tran  <br>max_fanout  <br>max_length |               | 0 (0)<br>0 (0)<br>0 (0)<br>0 (0) |              |                 | . 000<br>. 000<br>0        |                | 0 (0)<br>0 (0)<br>0 (0)<br>0 (0) | į                              |   |                          |

| nsity: 65.532%                                        |               |                                  |              |                 |                            | +              |                                  |                                |   |                          |

#### 9. Fill Insertion

• saveDesign test\_09\_fill.enc