## Homework Assignment 2 (Due 4:10pm, Feb. 4)

**[HSpice]** Download <a href="http://eecs.wsu.edu/~ee434/Homework/hw02.zip">http://eecs.wsu.edu/~ee434/Homework/hw02.zip</a>. Follow the instructions in hw00.pdf to source "ictools\_generic.sh" and "synopsys.sh". Open "inv.sp" in a text editor. Read all the lines carefully. The comments in the file give a brief overview of the HSpice syntax.

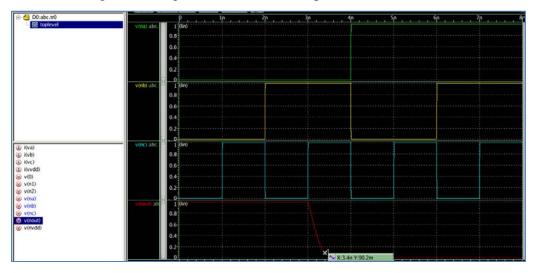

(1) [40 points] Create a netlist file for  $F = \overline{A + B \cdot C}$ . Set the lengths of all the FETs to 45nm. Set the widths of all the NFETs to 50nm. Set the widths of all the PFETs to 70nm. Add a 10fF capacitor to the output node. Simulate it using the following input stream (you should create three input voltage sources for yourself). ABC =  $(000) \rightarrow (001) \rightarrow (010) \rightarrow (011) \rightarrow (100) \rightarrow (101) \rightarrow (110) \rightarrow (111)$ . The input transition time should be 10ps. Give 990ps to each input combination so that the output can reach a sufficiently low or high voltage value whenever it switches.

**Submit**) A waveview snapshot of the waveforms of A, B, C, F. The delay values of all the rising and falling transitions at the output node.

Falling delay: 400ps