## Homework Assignment 5 (Due 5pm, Feb. 2, email to <a href="mailto:daehyun@eecs.wsu.edu">daehyun@eecs.wsu.edu</a>)

(1) [**Proof, 20 points**] A Boolean function can be expressed as a function of non-inverted and inverted inputs, AND operations, and OR operations as follows:

$$f(x_1, \overline{x_1}, x_2, \overline{x_2}, ..., x_n, \overline{x_n}, AND, OR).$$

For instance,  $Y = \overline{x_1 + x_2 \cdot x_3 + \overline{x_1} \cdot x_2 \cdot \overline{x_4}}$  is a Boolean function. Suppose  $F = f(x_1, \overline{x_1}, x_2, \overline{x_2}, \dots, x_n, \overline{x_n}, AND, OR)$  is expressed in inversion-of-sum-of-product form, i.e.,

$$F = \sum_{l=1}^{s} \left( \prod_{j=1}^{p_l} k_{l,j} \right) \tag{1}$$

where  $\Sigma$  is a sum (OR operations),  $\Pi$  is a product (AND operations), s is the number of product terms,  $p_i$  is the number of literals (a literal is a logic variable or its complement) in the i-th product term, and  $k_{i,j}$  is the j-th literal in the i-th product term  $(k_{i,j} \in \{x_1, \overline{x_1}, x_2, \overline{x_2}, ..., x_n, \overline{x_n}\})$ .

For  $Y = \overline{x_1 + x_2 \cdot x_3 + \overline{x_1} \cdot x_2 \cdot \overline{x_4}}$ , for example, s is 3 (there are three product terms  $(x_1, x_2 \cdot x_3, \overline{x_1} \cdot x_2 \cdot \overline{x_4})$ ,  $p_1 = 1, p_2 = 2, p_3 = 3$ ,  $k_{1,1} = x_1, k_{2,1} = x_2, k_{2,2} = x_3, k_{3,1} = \overline{x_1}, k_{3,2} = x_2, k_{3,3} = \overline{x_4}$ .

[Submit] Prove that implementing F in Equation (1) using the static CMOS design style requires maximum K NFETs and K PFETs where K is

$$K = \sum_{i=1}^{S} p_i.$$

Assume that all the non-inverted and inverted inputs are available for F.

Each product term is an ANDed term, i.e., the *i*-th product term is  $k_{i,1} \cdot k_{i,2} \cdot ... \cdot k_{i,p_i}$ , which can be implemented by a series connection of  $p_i$  number of NFETs. The inversion of the sum of the product terms can be implemented by a parallel connection of all the ANDed terms (series connections of the NFETs), so the total # NFETs is  $p_1 + p_2 + \cdots + p_s = \sum_{i=1}^s p_i$ . The PFET network can be implemented using the dual of the NFET network, so it requires the same number of NFETs.

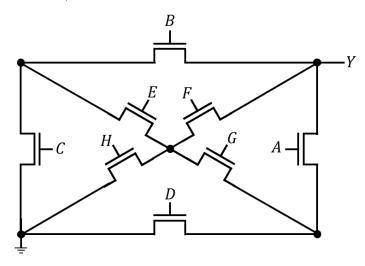

(2) [Analysis, 30 points] The following figures shows the NFET network of a logic gate. Y is the output and  $A \sim H$  are the inputs of the gate. Derive a Boolean equation as a function of the inputs for the output Y. (Hint: If you want, you can use HSpice to find Y).

$Y = \overline{AD + AGH + AGEC + BC + BEH + BEGD + FEC + FH + FGD}$