# Logic Design with MOSFETs

Dae Hyun Kim

EECS Washington State University

### References

- John P. Uyemura, "Introduction to VLSI Circuits and Systems," 2002.

Chapter 2

- Neil H. Weste and David M. Harris, "CMOS VLSI Design: A Circuits and Systems Perspective," 2011.

- Chapter 1

### Goal

• Design logic gates using MOSFETs (NMOS and PMOS)

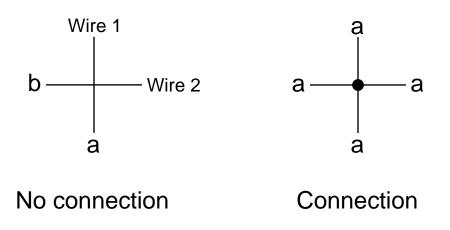

# **Signals and Wires**

• Signals

$$- 0 = V_{SS} = \text{Ground} = \text{GND} = \text{Low} = 0\text{V}$$

$-1 = V_{DD} = Power = PWR = High = 5V, 3.3V, 1.5V, 1.2V, 1.0V, etc.$

$V_{DD}$

• Wires

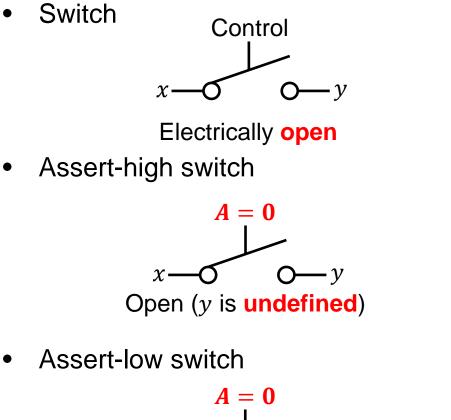

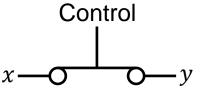

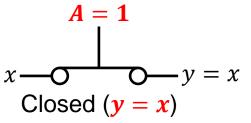

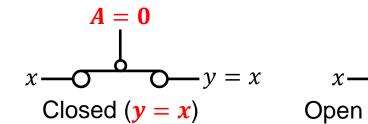

# **Ideal Switches**

Electrically short

•

Open (*y* is **undefined**)

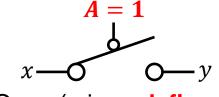

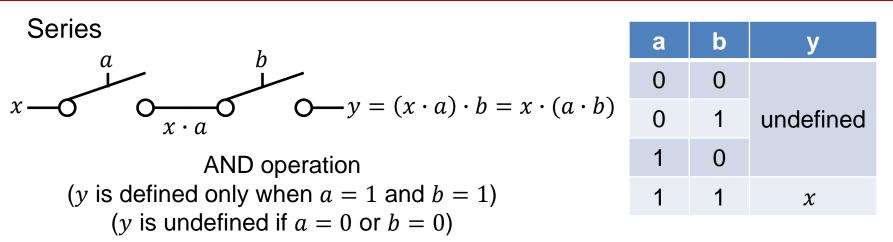

# **Series/Parallel Connections of Switches**

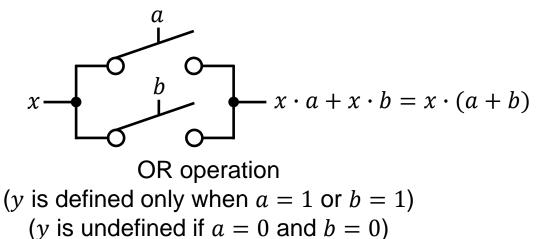

• Parallel

| а | b | у         |  |  |

|---|---|-----------|--|--|

| 0 | 0 | undefined |  |  |

| 0 | 1 |           |  |  |

| 1 | 0 | x         |  |  |

| 1 | 1 |           |  |  |

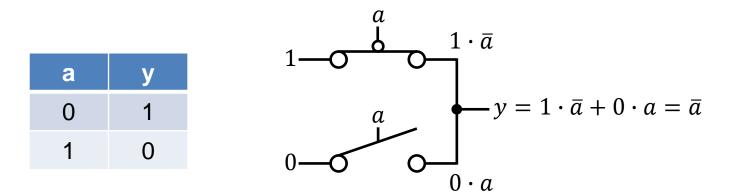

### **Inverter Design with Switches**

- Inverter

- The output is defined both when a = 0 and when a = 1.

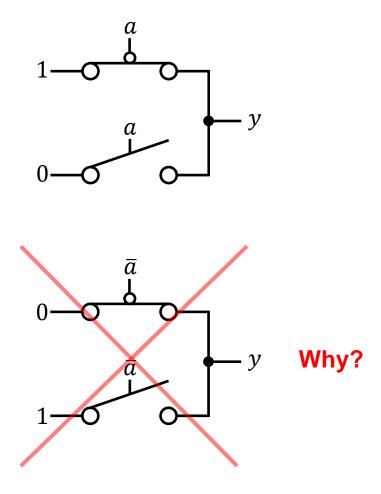

### **Inverter Design with Switches**

• Two inverter designs

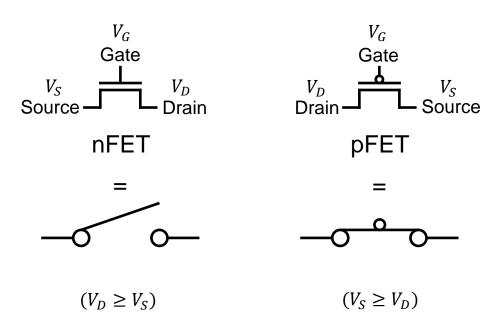

# **MOSFETs as Switches**

- MOSFET: Metal-Oxide-Semiconductor Field-Effect Transistor

- n-channel MOSFET = nFET = NMOS

- p-channel MOSFET = pFET = PMOS

- Complementary MOS: CMOS

- Symbols

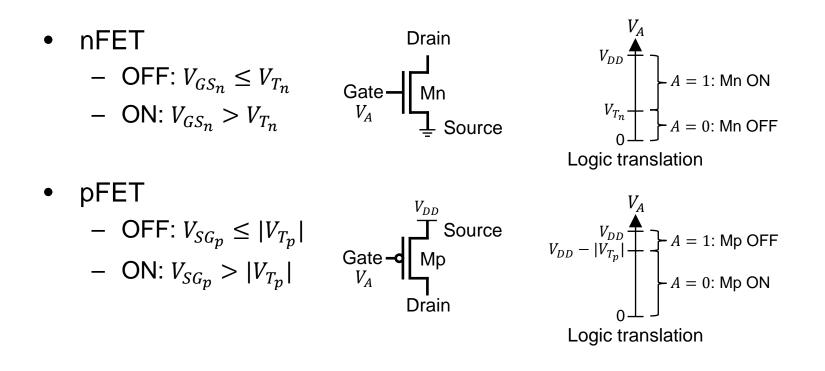

# **MOSFETs as Switches**

- Threshold voltage

- nFET:  $V_{T_n} > 0$

- pFET:  $V_{T_p} < 0$

# **MOSFETs as Switches**

- Example (PTM High-Performance 45nm High-K Metal Gate)

- *V<sub>DD</sub>*: 1.0V

- $V_{T_n}: 0.46893V$

- V<sub>Tp</sub>: -0.49158V

- Example (PTM High-Performance 32nm High-K Metal Gate)

- $V_{DD}: 0.9V$

- $V_{T_n}: 0.49396V$

- *V<sub>Tp</sub>*: -0.49155V

- Example (PTM High-Performance 22nm High-K Metal Gate)

- $V_{DD}: 0.8V$

- $V_{T_n}: 0.50308V$

- V<sub>Tp</sub>: -0.4606V

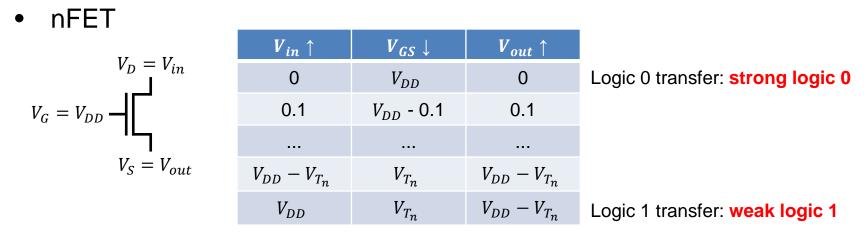

$V_{S} = V_{in}$   $V_{G} = 0 - \mathbf{q}$  $V_{in}\downarrow$  $V_{SG}\downarrow$  $V_{out} \downarrow$ Logic 1 transfer: strong logic 1  $V_{DD}$  $V_{DD}$  $V_{DD}$  $V_{DD} - \varepsilon$  $V_{DD} - \varepsilon$  $V_{DD} - \varepsilon$  $V_D = V_{out}$ ... ... ...  $|V_{T_p}|$  $|V_{T_p}|$  $|V_{T_p}|$ Logic 0 transfer: weak logic 0 0 0  $|V_{T_p}|$

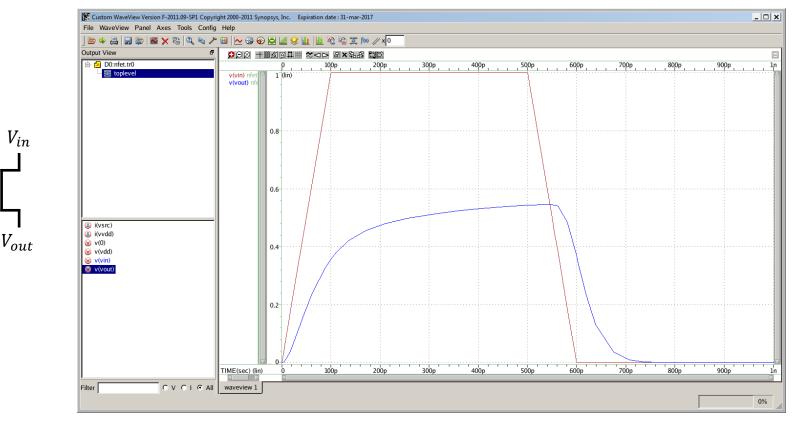

- SPICE simulation (45nm technology)

- nFET

$V_{DD}$ .

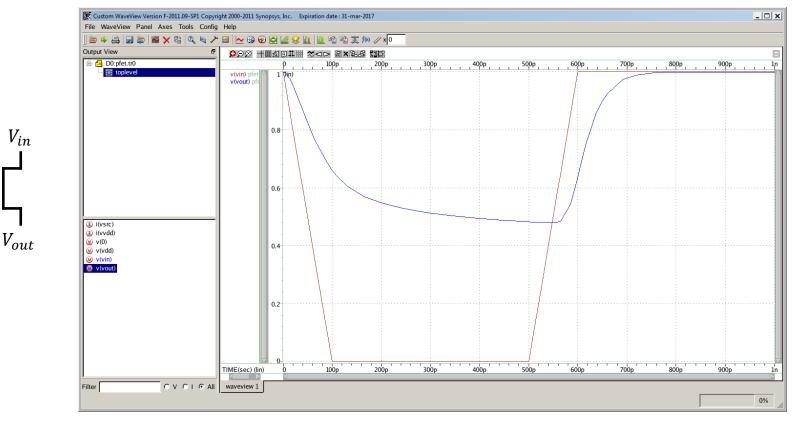

- SPICE simulation (45nm technology)

- pFET

- nFET

- Strong logic 0 transfer

- Weak logic 1 transfer

- pFET

- Strong logic 1 transfer

- Weak logic 0 transfer

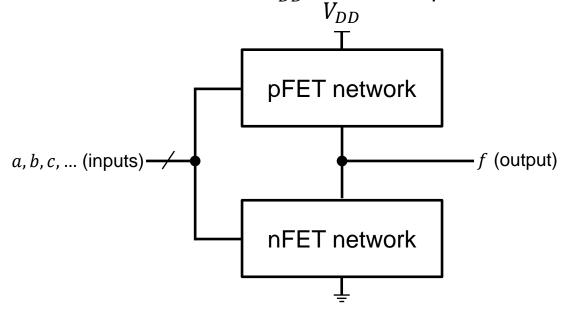

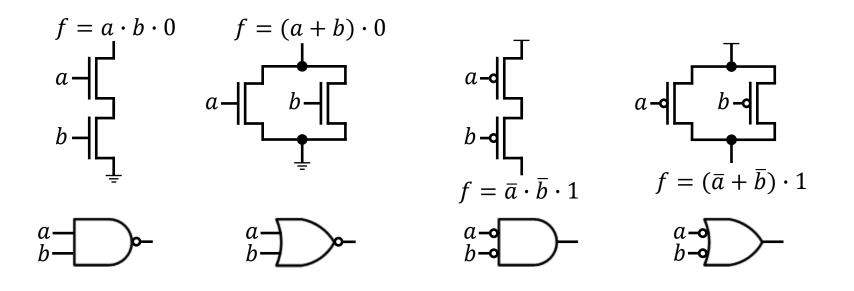

- CMOS

- Use pFETs to pass logic 1.

- Use nFETs to pass logic 0.

- Principles

- Construct the nFET network using only nFETs and the pFET network using only pFETs.

- If the output is 1, the pFET network connects  $V_{DD}$  to the output and the nFET network disconnects  $V_{SS}$  and the output.

- If the output is 0, the nFET network connects  $V_{SS}$  to the output and the pFET network disconnects  $V_{DD}$  and the output.

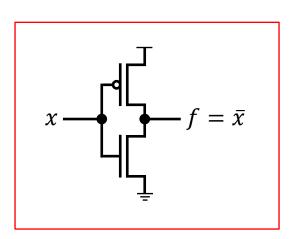

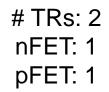

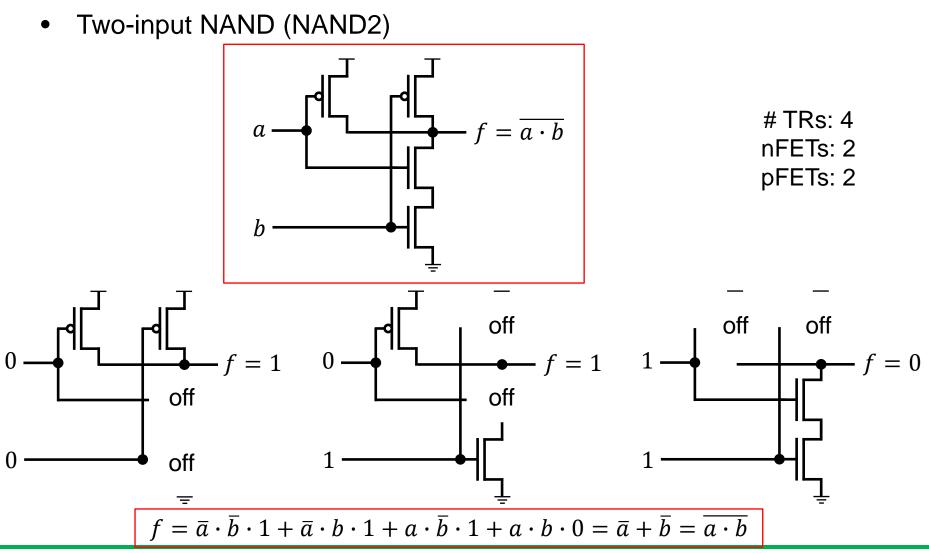

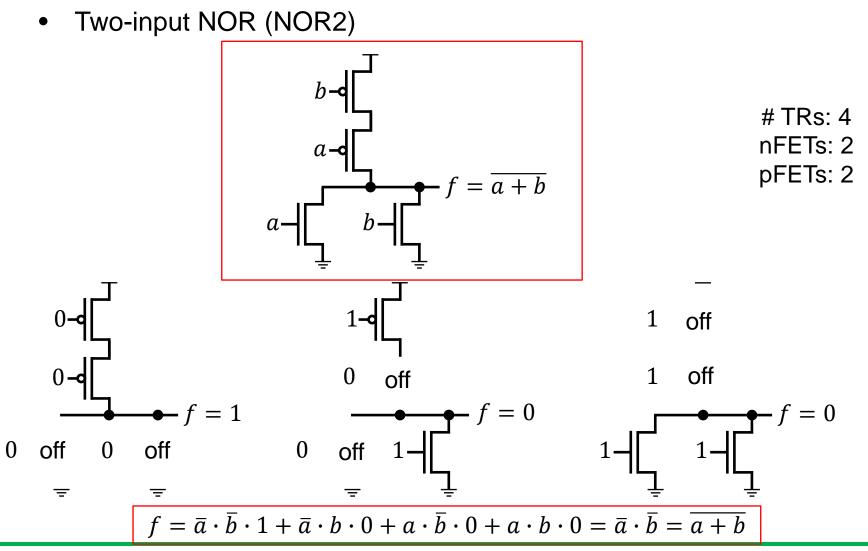

• Inverter

$f = \bar{x} \cdot 1 + x \cdot 0 = \bar{x}$

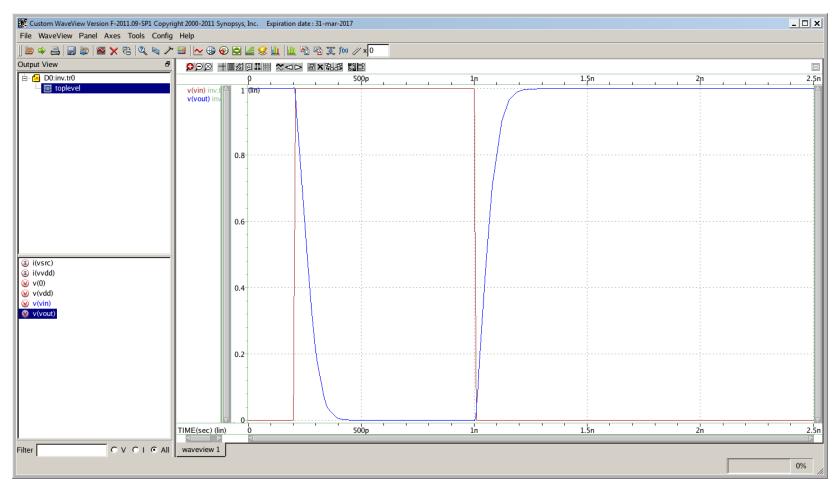

#### • SPICE simulation

#### • SPICE simulation

| Custom WaveView Version F-2011.09-SP1 Copyrig                        |                               | sys, Inc. Expiration da | ate : 31-mar-2017 |    |      |            | _ 🗆 🗙 |

|----------------------------------------------------------------------|-------------------------------|-------------------------|-------------------|----|------|------------|-------|

| File WaveView Panel Axes Tools Config                                |                               |                         |                   |    |      |            |       |

| 🔄 🌳 📇    🔜 😂  🚟 🗙 🕄 🔍 🔌 🥕                                            | 🔠 🗠 😌 🌚 😫                     | 2 🖉 😢 🏨 🖣               | 🛍 🗟 🦉 f(x) 🥢 x 🛛  |    |      |            |       |

| Output View 🗗                                                        |                               | ⊴p∎ ≈⊲⊳                 | SX94 BC           |    |      |            |       |

| È- 🚰 D0:nand2.tr0<br>└── 💽 toplevel                                  |                               | ρ<br>1 (lin)<br>).8     | 500p              | 1n |      | <u>2</u> n | 2.5r  |

|                                                                      |                               | 0.6                     |                   |    |      |            |       |

|                                                                      |                               | ).4                     |                   |    |      |            |       |

| (2) i(vsrc1)<br>(2) i(vsrc2)<br>(2) i(vvdd)<br>(2) v(0)<br>(2) v(n1) |                               | <br>1_(lin)<br>).8      |                   |    |      |            |       |

|                                                                      |                               | ).6                     |                   |    |      |            |       |

|                                                                      |                               | ).2                     |                   |    |      |            |       |

|                                                                      |                               | 0<br>1 ((in)<br>).8     |                   |    |      |            |       |

|                                                                      |                               | ).6                     |                   |    |      |            |       |

|                                                                      |                               | ).2<br>.2               |                   |    |      |            |       |

| ilter CVCI © All                                                     | TIME(sec) (lin)<br>waveview 1 | 0                       | 500p              | 1n | 1.5n | 2n         | 2.5   |

|                                                                      |                               |                         |                   |    |      |            | 0%    |

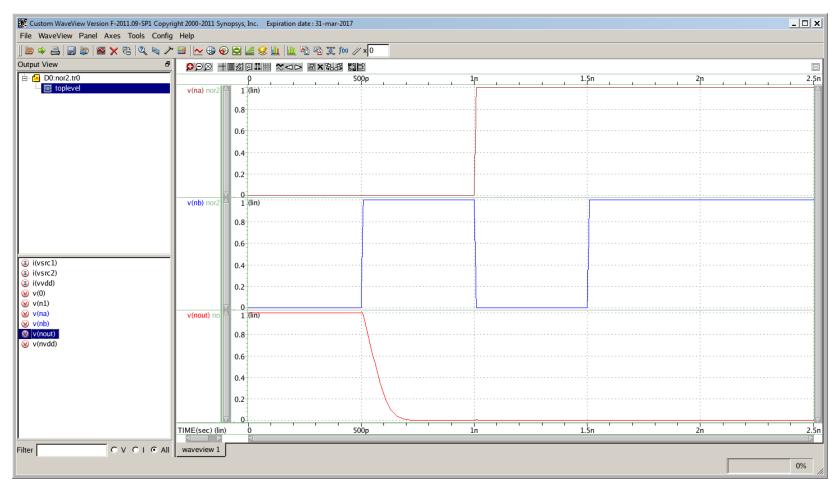

#### • SPICE simulation

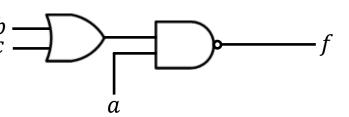

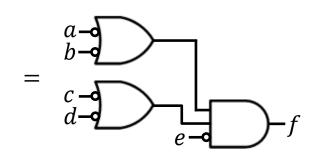

• Example

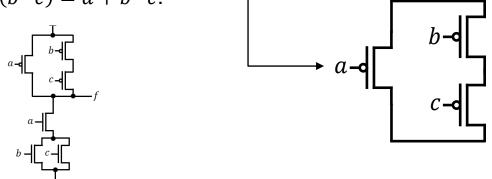

$$f = \overline{a \cdot (b+c)}$$

• Using logic gates

# TRs: 14 nFETs: 7 pFETs: 7

# TRs: 10

nFETs: 5

pFETs: 5

• Using logic gates

• Using TRs

- # TRs: 6 nFETs: 3

- pFETs: 3

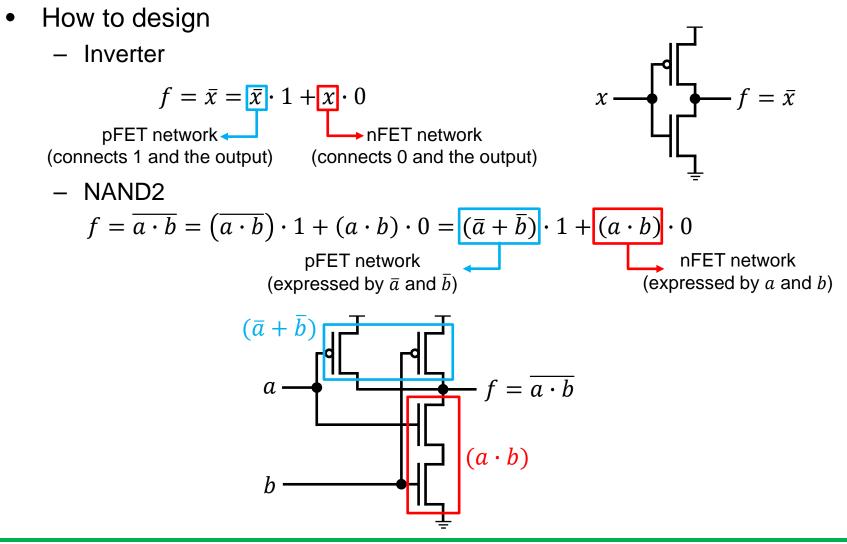

- How to design f

- Express  $f = A \cdot 1 + B \cdot 0 = F(\overline{x_1}, ..., \overline{x_n}) \cdot 1 + \overline{F(x_1, ..., x_n)} \cdot 0$

- Design a pFET network using  $A = F(\overline{x_1}, ..., \overline{x_n})$ .

- pFETs are ON when the inputs are 0.

- Design an nFET network using  $B = \overline{F(x_1, ..., x_n)}$ .

- nFETs are ON when the inputs are 1.

- Example

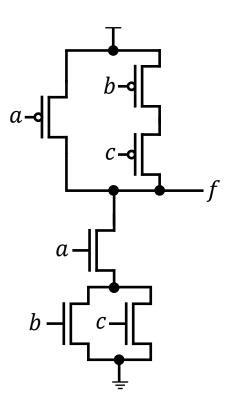

$$f = \overline{a \cdot (b + c)}$$

$$- f = \overline{a \cdot (b + c)} \cdot 1 + a \cdot (b + c) \cdot 0 = \underbrace{(\overline{a} + \overline{b} \cdot \overline{c})}_{\text{pFET network}} \cdot 1 + \underbrace{a \cdot (b + c)}_{\text{nFET network}} \cdot 0$$

$$a - \underbrace{\left(\begin{array}{c} b - 4 \\ c - 4 \end{array}\right)}_{\text{pFET network}} \cdot 1 + \underbrace{a \cdot (b + c)}_{\text{nFET network}} \cdot 0$$

• Example

$$f = \overline{a \cdot (b+c)}$$

# TRs: 6 nFETs: 3 pFETs: 3

- Structured logic design

- Design a given Boolean equation using nFETs and pFETs.

- Assume that only non-inverted input signals are given.

- *a*, *b*, *c*, ... are given.

- $-\bar{a}, \bar{b}, \bar{c}, ...$  are not given. If you need them, you should generate them.

- Design methodology 1

- When  $f = \overline{S(x_1, ..., x_n)}$  (S is a function of non-inverted variables)

- $f = \overline{S} = \overline{S} \cdot 1 + S \cdot 0$

- Design an nFET network for S using  $x_1, ..., x_n$ .

- Design a pFET network for  $\overline{S}$  using  $\overline{x_1}, \dots, \overline{x_n}$ .

- Connect them to  $V_{DD}$ ,  $V_{SS}$ , f.

- Example:  $f = \overline{a \cdot (b + c)}$

- $f = \overline{a \cdot (b+c)} \cdot 1 + a \cdot (b+c) \cdot 0$

- Design an nFET network for  $a \cdot (b + c)$ .

- Design a pFET network for  $\overline{a \cdot (b+c)} = \overline{a} + \overline{b} \cdot \overline{c}$ . -

- Connect them.

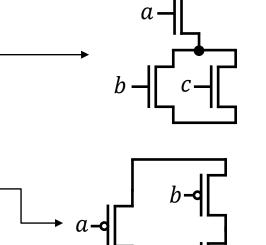

- Design methodology 2

- When  $f = \overline{S(x_1, \dots, x_n)}$

- $f = \overline{S} = \overline{S} \cdot 1 + S \cdot 0$

- Design an nFET network for *S*.

- Design a pFET network with a dual logic of the nFET network.

- Dual of  $f(x_1, ..., x_n, 0, 1, AND, OR) = f(x_1, ..., x_n, 1, 0, OR, AND)$

- Connect them.

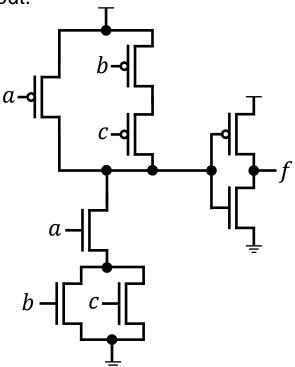

- Example:

$$f = \overline{a \cdot (b+c)}$$

- $f = \overline{a \cdot (b+c)} \cdot 1 + a \cdot (b+c) \cdot 0$

- Design an nFET network for  $a \cdot (b + c)$ . -

- Dual of  $a \cdot (b + c) = a + (b \cdot c) = a + b \cdot c$ . —

- Connect them.

- Dual logic

- $f(x_1, ..., x_n, 0, 1, AND, OR)^D = f(x_1, ..., x_n, 1, 0, OR, AND)$

- Example

- $(A \cdot B)^D = A + B$

- $(A+B)^D = A \cdot B$

- $(1 \cdot A)^D = 0 + A = A$

- $(1+A)^D = 0 \cdot A = 0$

- $(0 \cdot A)^D = 1 + A = 1$

- $(0+A)^D = 1 \cdot A = A$

- Principles of the dual logic

- The nFET and the pFET networks work complementarily.

- If the nFET network is ON (i.e., connects  $V_{SS}$  to the output), the pFET network is OFF (i.e., disconnect the output from  $V_{DD}$ ) and vice versa.

- If two networks are dual, they work complementarily.

- Prove!

• Principles of the dual logic

$$- f = \overline{S(x_1, \dots, x_n)} = f = \overline{S(x_1, \dots, x_n)} \cdot 1 + S(x_1, \dots, x_n) \cdot 0$$

- $-\overline{S(x_1, \dots, x_n)} = \overline{S(x_1, \dots, x_n, 0, 1, AND, OR)} = S(\overline{x_1}, \dots, \overline{x_n}, 1, 0, OR, AND) = S(\overline{x_1}, \dots, \overline{x_n})^D$  (De Morgan's law)

- A pFET is ON when its control variable  $(x_i)$  is 0.

- Thus, the pFET network is the dual of the nFET network.

- Design methodology 3

- When  $f = S(x_1, ..., x_n)$  (S is a function of non-inverted variables)

- $f = S = \overline{\bar{S}}$

- Design  $\overline{S}$  and add an inverter at the output.

- Example:  $f = a \cdot (b + c)$

- $f = a \cdot (b + c) = \overline{\overline{a \cdot (b + c)}}$

- Design  $\overline{a \cdot (b+c)}$ .

- Add an inverter at the output.

- Design methodology 4

- When  $f = \overline{S(\overline{x_1}, ..., \overline{x_n})}$  (*S* is a function of inverted variables)

- Generate inverted inputs  $(\overline{x_1}, ..., \overline{x_n})$  from the given inputs  $(x_1, ..., x_n)$ .

- Design *S* using the inverted inputs.

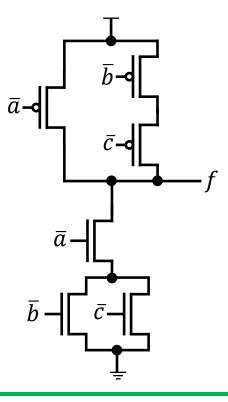

- Example:  $f = \overline{\overline{a} \cdot (\overline{b} + \overline{c})}$

- Inverters are not shown for brevity.

- Design methodology 5

- When  $f = \overline{S(\overline{x_1}, \dots, \overline{x_n})}$

- $f = \overline{S(\overline{x_1}, \dots, \overline{x_n})} = S(x_1, \dots, x_n)^D = \overline{\overline{S(x_1, \dots, x_n)^D}}$

- Design  $\overline{S(x_1, \dots, x_n)^D}$  using the given inputs.

- Add an inverter at the output.

- Example:  $f = \overline{\overline{a} + (\overline{b} \cdot \overline{c})}$

•

$$f = a \cdot (b + c) = \overline{a \cdot (b + c)}$$

- Design methodology 6

- When  $f = S(\overline{x_1}, ..., \overline{x_n})$

- $f = S = \overline{\bar{S}}$

- Generate inverted inputs  $(\overline{x_1}, ..., \overline{x_n})$  from the given inputs  $(x_1, ..., x_n)$ .

- Design  $\overline{S}$  using the inverted inputs and add an inverter at the output.

- Design methodology 7

- When  $f = S(\overline{x_1}, ..., \overline{x_n})$

- $f = \overline{\overline{S(\overline{x_1}, \dots, \overline{x_n})}} = \overline{S(x_1, \dots, x_n)^D}$

- Design  $S^D$  using the given non-inverted inputs  $(x_1, ..., x_n)$ .

- Design methodology 8

- When  $f = S(x_1, \overline{x_1}, ..., \overline{x_n})$  or  $\overline{S(x_1, \overline{x_1}, ..., \overline{x_n})}$

- Convert the given function into an appropriate form to simplify the logic.

- Design it.

• Examples (assuming only non-inverted inputs are available)

$- f = a \cdot b$  (AND2)

- Design  $f = \overline{a \cdot b}$  and add an inverter at the output. (# TRs: 6)

- Design  $f = \overline{\overline{a \cdot b}} = \overline{\overline{a + \overline{b}}}$  with two inverters to generate  $\overline{a}$  and  $\overline{b}$ . (# TRs: 8)

- $f = \overline{\overline{a} \cdot b + \overline{c} \cdot d}$

- Add two inverters to generate  $\bar{a}$  and  $\bar{c}$ , then design f. (# TRs: 12)

$$- f = \bar{s} \cdot a + s \cdot b$$

(2:1 MUX)

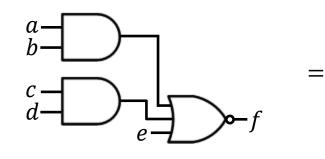

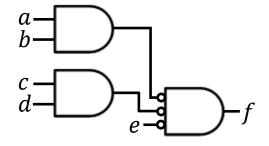

• Bubble pushing (how to construct a pFET network) -  $f = A \cdot 1 + B \cdot 0 = F(\overline{x_1}, ..., \overline{x_n}) \cdot 1 + F(x_1, ..., x_n)^D \cdot 0$

- Bubble pushing (how to construct a pFET network)

- Example

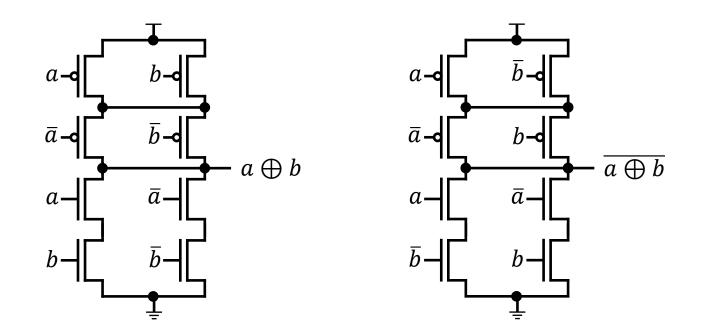

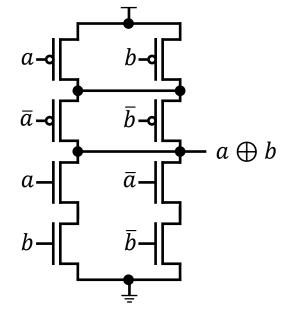

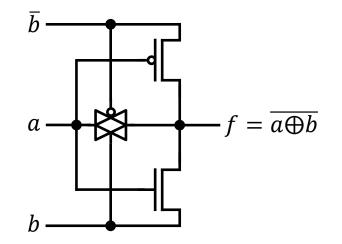

• XOR

$- a \oplus b = a \cdot \overline{b} + \overline{a} \cdot b = \overline{a \cdot b + \overline{a} \cdot \overline{b}}$ (#TRs: 8+4(for the two inverters))

- XNOR

- $\overline{a \oplus b} = a \cdot b + \overline{a} \cdot \overline{b} = \overline{a \cdot \overline{b} + \overline{a} \cdot b}$ (#TRs: 8+4(for the two inverters))

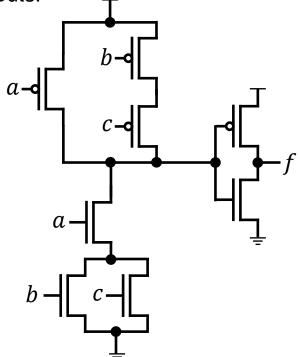

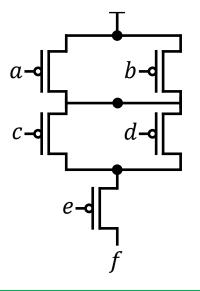

- Structured logic analysis

- Derive a Boolean equation for a given transistor-level schematic.

- Analysis methodology 1

- Convert the nFET network into a Boolean equation (only when the pFET network is the dual of the nFET network.)

- Notice that the nFET network passes logic 0.

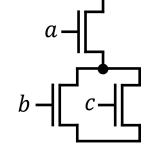

- Example

$$- f = \overline{a \cdot b + \overline{a} \cdot \overline{b}} = (\overline{a} + \overline{b}) \cdot (a + b) = a \cdot \overline{b} + \overline{a} \cdot b$$

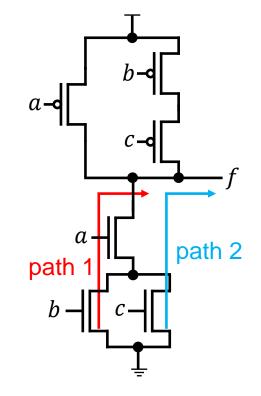

- Analysis methodology 2

- Identify all the paths from  $V_{SS}$  to the output (only when the pFET network is the dual of the nFET network.)

- Merge them into a single Boolean equation.

- Negate the output.

- Example

- Path 1:  $b \cdot a$

- Path 2:  $c \cdot a$

- Merge:  $b \cdot a + c \cdot a = a \cdot (b + c)$

- Negate:  $\overline{a \cdot (b+c)}$

$$- f = \overline{a \cdot (b+c)}$$

#### **Pass Transistors**

- nFET

- g = 0: OFF

- -g = 1: ON

- a = 0: b = strong 0• a = 1: b = weak 1

- pFET

- g = 1: OFF

- g = 0: ON

•

$$a = 0$$

:  $b = \text{weak } 0$

•  $a = 1$ :  $b = \text{strong } 1$   $a \checkmark b$

g

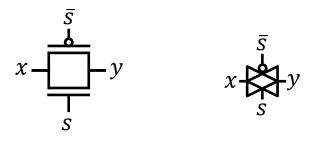

### **Transmission Gate Circuits**

• Transistor circuit

- Behaviors

- When s = 0: Both nFET and pFET are OFF.

- When s = 1: Both nFET and pFET are ON.

- If x = 0, the nFET perfectly transmits it to y (nFET is good at transferring 0.)

- If x = 1, the pFET perfectly transmits it to y (pFET is good at transferring 1.)

- Disadvantage

- Needs  $\bar{s}$ .

- Does not restore the input signals.

#### **Transmission Gate Circuits**

• Logic design using transmission gates

- MUX:

$$f = \overline{s} \cdot x_0 + s \cdot x_1$$

$$x_0 \xrightarrow{S}{\overline{s}} f$$

#### **Pass Transistors vs. Transmission Gates**

|                 | Pass TR.           |                    | Transmission Gates   |

|-----------------|--------------------|--------------------|----------------------|

| Symbols         | <u>ب</u> لار       | <u> </u>           | ₿                    |

| Signal strength | Strong 0<br>Weak 1 | Weak 0<br>Strong 1 | Strong 0<br>Strong 1 |

| Area            | A                  | rA(r > 1)          | (1 + r)A             |

| Control signal  | g                  | g                  | $g$ , $ar{g}$        |

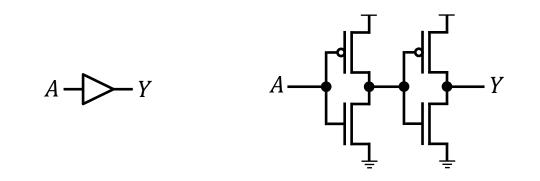

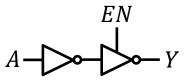

### **Buffer**

• Y = A

- Buffers are used for

- Signal restoration

- Interconnect optimization

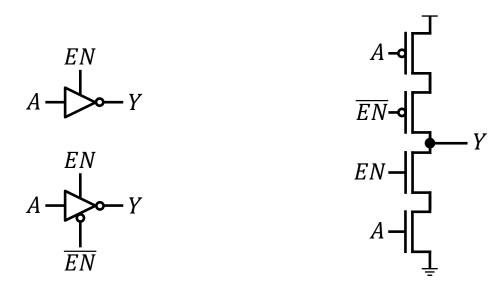

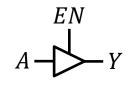

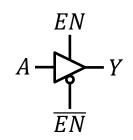

#### **Tristate Inverter**

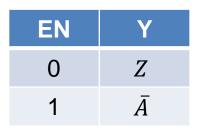

• Truth table

• Symbol & Schematic

# **Tristate Buffer**

• Symbol

• Gate-level schematic

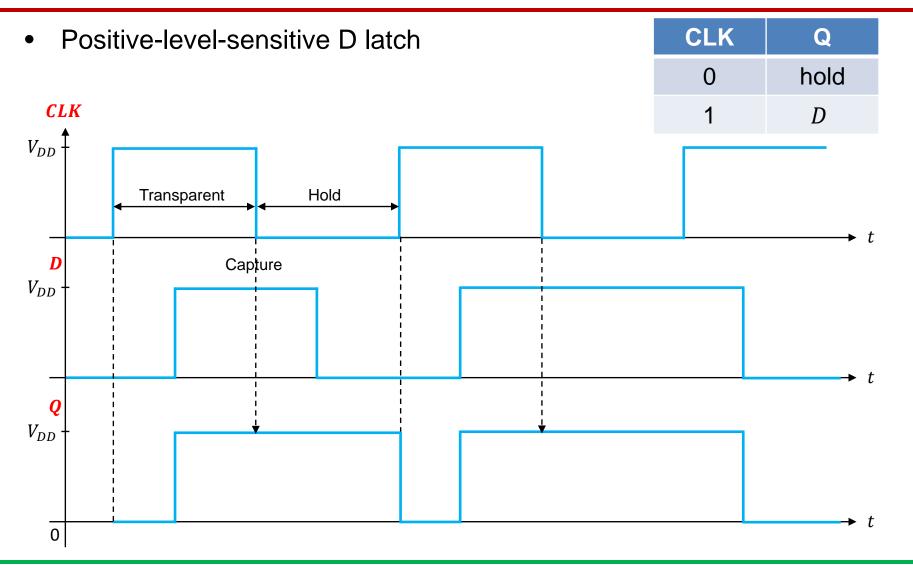

# **Sequential Circuit – D Latch**

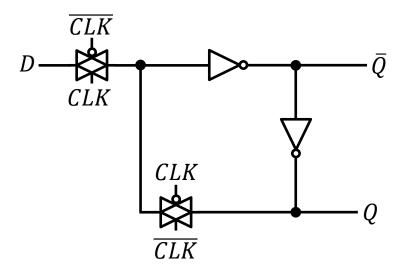

### **Sequential Circuit – D Latch**

• Schematic

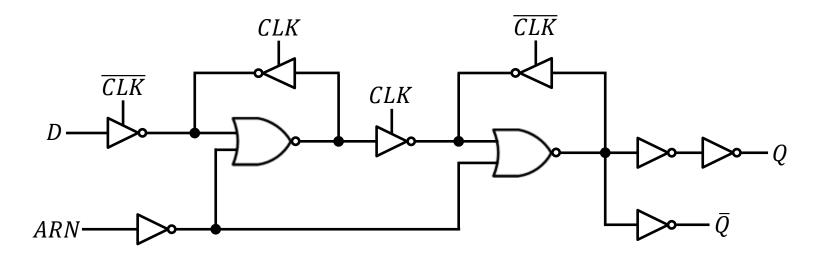

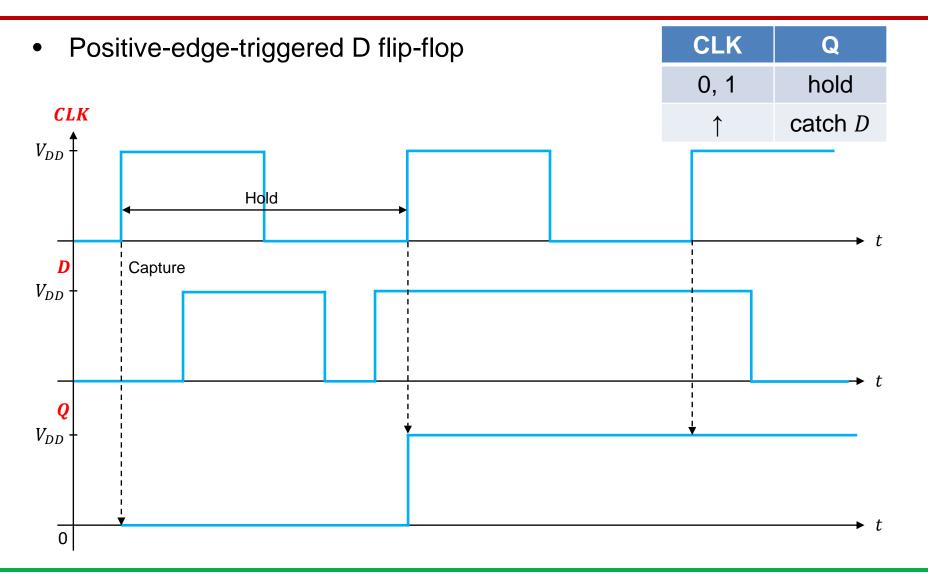

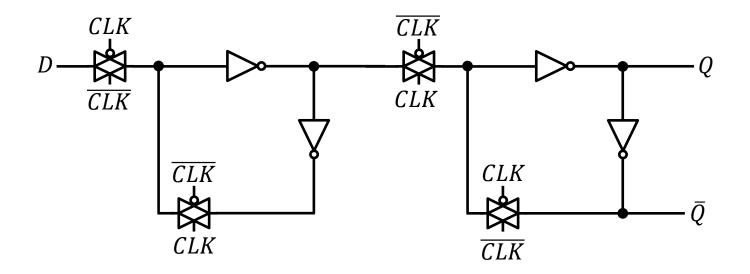

# **Sequential Circuit – D Flip-Flop**

# **Sequential Circuit – D Flip-Flop**

• Schematic

# **Sequential Circuit**

- Example

- Inputs: *D*, *ARN*, *CLK*, *CLK*

- Outputs:  $Q, \overline{Q}$