# EE434 ASIC and Digital Systems

## **Final Exam**

May 1, 2019. (8am – 10am)

Instructor: Dae Hyun Kim (daehyun@eecs.wsu.edu)

Name:

WSU ID:

| Problem | Points |  |

|---------|--------|--|

| 1       | 20     |  |

| 2       | 20     |  |

| 3       | 30     |  |

| 4       | 20     |  |

| 5       | 20     |  |

| 6       | 20     |  |

| 7       | 20     |  |

| 8       | 20     |  |

| Total   | 170    |  |

#### **Problem #1 (Static Timing Analysis, 20 points)**

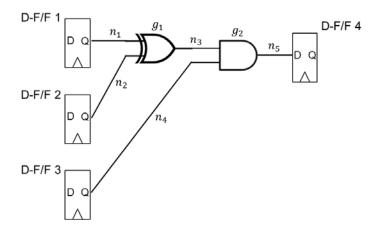

The following shows a pipeline stage. D-FF1, D-FF2, and D-FF3 are stage-k D-FFs and D-FF4 is a stage-(k+1) D-FF.  $n_i$  and  $g_m$  are net and gate delays, respectively.

The properties of D-FFp ( $p = 1 \sim 4$ ) are as follows:

- Setup time:  $s_p$  (for example,  $s_3$  is the setup time of D-FF3.)

- Hold time:  $h_p$  (for example,  $h_2$  is the hold time of D-FF2.)

- C-Q delay:  $c_p$  (for example,  $c_1$  is the C-Q delay of D-FF1.)

- Delay from the clock source to the clock pin of D-FFp:  $d_p$  (e.g.,  $d_4$  is the delay from the clock source to the clock pin of D-FF4.)

$T_{CLK}$  is the clock period. You can also use the "MAX" and "MIN" operators.

MAX(a, b) = a (if a>b) or b (otherwise). MIN(a, b) = a (if a<b) or b (otherwise).

(1) Find all inequalities for the setup time constraints of the system shown above.

$$MAX\{MAX(d_1 + c_1 + n_1, d_2 + c_2 + n_2) + g_1 + n_3, d_3 + c_3 + n_4\} + g_2 + n_5 \le d_4 + T_{CLK} - s_4$$

(2) Find all inequalities for the hold time constraints of the system shown above.

$$MIN\{MIN(d_1 + c_1 + n_1, d_2 + c_2 + n_2) + g_1 + n_3, d_3 + c_3 + n_4\} + g_2 + n_5 \ge d_4 + h_4$$

#### Problem #2 (STA & Power, 20 points)

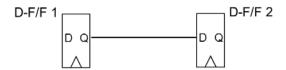

The output Q of D-FF 1 is directly connected to the input D of D-FF 2. The length of the net is negligible, so the net delay is zero.

- *T<sub>skew</sub>*: 0ps

- T<sub>h2</sub> (the hold time of D-FF 2): 40ps

- $T_{CO1}$ (the clock-to-Q delay of D-FF 1): 10ps

- Available buffers: BUF X1, BUF X2, BUF X4

- The input and output capacitance of a buffer: negligible (0 fF)

- The internal delay of a buffer BUF\_Xs:  $\frac{12}{s}$  ps (for example, the internal delay of a buffer BUF\_X2 is 12/2=6ps.)

- The power consumption of a buffer BUF\_Xs:  $10 \cdot s + 20$  (nW) (for example, the power consumption of a BUF\_X2 is 40 nW.)

You are supposed to insert buffers into the net so that you can satisfy the hold time constraint and minimize the total power consumption. Find how many buffers you should insert into the net.

Hold time constraint:  $d_1 + T_{CQ1} + T_{logic} \ge d_2 + T_{h2} \iff T_{logic} \ge 30ps$

Suppose we insert #a BUF\_X1, #b BUF\_X2, #c BUF\_X4 buffers. Then, the total logic delay is 12a + 6b + 4c.  $12a + 6b + 4c \ge 30$ , so  $6a + 3b + 2c \ge 15$ .

The total power consumption is (30a + 40b + 60c) nW.

Let's enumerate all the possibilities for (a, b, c) and get their power values.

```

(0,0,8): 480nW, (0,1,6): 400nW, (0,2,5): 380nW, (0,3,3): 300nW, (0,4,2): 280nW, (0,5,0): 200nW. (1,0,5): 330nW, (1,1,3): 250nW, (1,2,2): 230nW, (1,3,0): 150nW (2,0,2): 180nW, (2,1,0): 100nW, (3,0,0): 90nW

```

# BUF\_X1: 3

# BUF X2: 0

# BUF X4: 0

## Problem #3 (STA, 30 points)

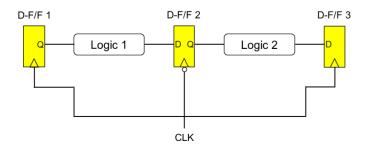

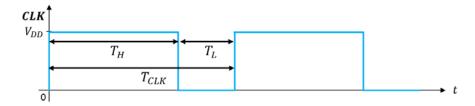

The following figure shows two pipeline stages. Notice that D-FF 1 and D-FF 3 are positive-edge-triggered FFs, whereas D-FF 2 is a negative-edge-triggered FF.

The following shows the waveform of the clock.

Notice that the duty cycle of the clock (=  $T_H/T_{CLK}$ ) is not 50%.

- Delay from the clock source to D-FF 1, 2, 3:  $d_1$ ,  $d_2$ ,  $d_3$

- C-Q delay of D-FF 1, 2, 3:  $c_1$ ,  $c_2$ ,  $c_3$

- Delay of Logic 1 and Logic 2: T<sub>1</sub>, T<sub>2</sub>

- Setup time of D-FF 1, 2, 3:  $s_1$ ,  $s_2$ ,  $s_3$

- Hold time of D-FF 1, 2, 3:  $h_1$ ,  $h_2$ ,  $h_3$

- (1) Find all inequalities for the setup time constraints of the system shown above.

$$d_1 + c_1 + T_1 \le d_2 + T_H - s_2$$

$$d_2 + c_2 + T_2 + T_H \le d_3 + T_{CLK} - s_3 \iff d_2 + c_2 + T_2 \le d_3 + T_L - s_3$$

(2) Find all inequalities for the hold time constraints of the system shown above.

$$d_1 + T_{CLK} + c_1 + T_1 \ge d_2 + T_{CLK} - T_L + h_2 \iff d_1 + c_1 + T_1 \ge d_2 - T_L + h_2$$

$$d_2 + T_{CLK} + T_H + c_2 + T_2 \ge d_3 + T_{CLK} + h_3 \iff d_2 + T_H + c_2 + T_2 \ge d_3 + h_3$$

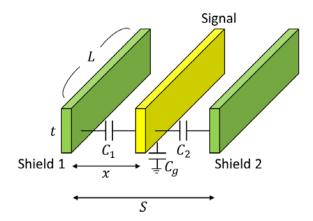

#### Problem #4 (Coupling, 20 points)

The following figure shows a signal net surrounded by two shield nets (Shield 1 and Shield 2) that are grounded. The coupling caps between Shield 1 and the signal net and between the signal net and Shield 2 are  $C_1$  and  $C_2$ , respectively.

- Delay of the signal net:  $(R + 0.5rL) \cdot (C_g + C_1 + C_2)$

- R (constant): The output resistance of the driver driving the signal net

- r (constant): Unit wire resistance

- L (constant): The length of the wires

- t (constant): The thickness of the wires

- S (constant): The distance between Shield 1 and Shield 2

- $C_q$  (constant): The ground cap of the signal net

- $\epsilon$  (constant): Permittivity of the insulator material

- x (variable): The distance between Shield 1 and the signal net

- $C_1 = \frac{\epsilon tL}{x}$ ,  $C_2 = \frac{\epsilon tL}{S-x}$

Find x that minimizes the delay of the signal net (you should express the optimal value of x as a function of some of the constants given above).

Delay

$$D=(R+0.5rL)\cdot (C_g+\frac{\epsilon tL}{x}+\frac{\epsilon tL}{(S-x)})$$

$$\frac{dD}{dx}=(R+0.5rL)\cdot \left(-\frac{\epsilon tL}{x^2}+\frac{\epsilon tL}{(S-x)^2}\right)=0$$

$$x=S-x$$

$$x=\frac{S}{2}$$

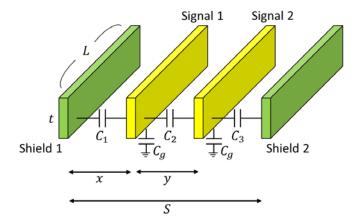

## Problem #5 (Coupling, 20 points)

This problem is similar to Problem #4, but now we will consider two signal nets as follows.

- Delay of Signal 1:  $(R + 0.5rL) \cdot (C_g + C_1 + 2C_2)$

- Delay of Signal 2:  $(R + 0.5rL) \cdot (C_g + C_3 + 2C_2)$

- x (variable): The distance between Shield 1 and Signal 1

- y (variable): The distance between Signal 1 and Signal 2

- $C_1 = \frac{\epsilon tL}{x}$ ,  $C_2 = \frac{\epsilon tL}{y}$ ,  $C_3 = \frac{\epsilon tL}{S (x + y)}$

Find x and y that minimize the sum of the delays of the two signal nets (you should express the optimal values of x and y as functions of some of the constants given above).

Sum of the delays

$$D = (R + 0.5rL) \cdot (2C_g + \frac{\epsilon tL}{x} + \frac{\epsilon tL}{S - (x + y)} + 4\frac{\epsilon tL}{y})$$

1) Since the structure is symmetric, we can use = S - (x + y). y = S - 2x.

$$\frac{dD}{dx} = (R + 0.5rL) \cdot \left( -2\frac{\epsilon tL}{x^2} + \frac{8\epsilon tL}{(S - 2x)^2} \right) = 0.$$

$$4x^2 = (S - 2x)^2 \cdot x = \frac{S}{4} \cdot y = \frac{S}{2}.$$

2)

$$\frac{\partial D}{\partial x} = (R + 0.5rL) \cdot \left( -\frac{\epsilon tL}{x^2} + \frac{\epsilon tL}{\left(S - (x+y)\right)^2} \right) = 0$$

. From this, we get  $x = S - (x+y)$ .

$$\frac{\partial D}{\partial y} = (R + 0.5rL) \cdot \left(\frac{\epsilon tL}{\left(S - (x + y)\right)^2} - 4\frac{\epsilon tL}{y^2}\right) = 0. \text{ From this, we get } S - (x + y) = \frac{y}{2}.$$

From them, we get

$$x = \frac{s}{4}$$

.  $y = \frac{s}{2}$ .

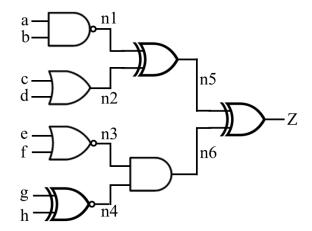

### Problem #6 (Testing, 20 points)

1) Find all test vectors that can detect a s-a-0 fault at input f. (You can use X for don't-cares).

$$X \oplus X_F = 1.$$

$$X = \{ \overline{a \cdot b} \oplus (c + d) \} \oplus \{ \overline{e + f} \cdot \overline{g \oplus h} \}$$

$$X_F = \{ \overline{a \cdot b} \oplus (c + d) \} \oplus \{ \overline{e} \cdot \overline{g \oplus h} \}$$

f=1. Then,  $\overline{e+f}=0$ . Thus, e=0. Then,  $=\{\overline{a\cdot b}\oplus(c+d)\}\oplus\{0\}$ .  $X_F=\{\overline{a\cdot b}\oplus(c+d)\}\oplus\{\overline{g\oplus h}\}$ . Therefore,  $\overline{g\oplus h}=1$ , i.e., (g,h)=(0,0) or (1,1).

Now,  $X = \{\overline{a \cdot b} \oplus (c + d)\}$ .  $X_F = \{\overline{a \cdot b} \oplus (c + d)\}$ . Thus,  $X \oplus X_F = 1$  for any a, b, c, d.

Answer: (XXXX0100) or (XXXX0111).

2) Find all test vectors that can detect a s-a-1 fault at node n3. (You can use X for don't-cares).

$$X_F = \{\overline{a \cdot b} \oplus (c+d)\} \oplus \{1 \cdot \overline{g \oplus h}\} = \{\overline{a \cdot b} \oplus (c+d)\} \oplus \{\overline{g \oplus h}\}$$

Thus,  $\overline{g \oplus h} = 1$  and  $\overline{e+f} = 0$ . From the former, we get (g,h) = (0,0) or (1,1). From the latter, we get (e,f) = (0,1) or (1,0) or (1,1).

Answer: (*XXXX*0100) or (*XXXX*0111) or (*XXXX*1000) or (*XXXX*1011) or (*XXXX*1100) or (*XXXX*1111).

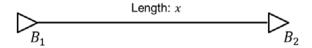

#### Problem #7 (Interconnects, 20 points)

The following figure shows a buffer (B1) driving a buffer (B2). We can route the net through a lower metal layer such as metal layer 1 or an upper metal layer such as metal layer 6. The following shows the properties of the two metal layers.

|                                 | Metal layer 1 | Metal layer 6 |

|---------------------------------|---------------|---------------|

| Resistivity                     | ρ             |               |

| Permittivity                    | 3             |               |

| Thickness                       | t             | $k_1 \cdot t$ |

| Width                           | W             | $k_2 \cdot w$ |

| Spacing between two metal wires | S             | $k_3 \cdot s$ |

The wire is sufficiently long, so you can ignore the input capacitance of B2. You can also assume that the output resistance of B1 is very small (almost zero ohm).

Problem: Suppose  $\tau_1$  and  $\tau_2$  are the delays of the net routed in metal layer 1 and metal layer 6, respectively. If  $k_1=2$ ,  $k_2=4$ ,  $k_3=2$ , what is the ratio between  $\tau_1$  and  $\tau_2$ ?

$$\tau_1 = \frac{1}{2}r_1c_1x^2$$

where  $c_1 = \varepsilon \frac{t}{s}$ .  $r_1 = \rho \frac{1}{wt}$ .

$$au_2=rac{1}{2}r_2c_2x^2$$

where  $c_2=arepsilonrac{k_1t}{k_3s}$ .  $r_2=

horac{1}{k_1k_2wt}$ .

Thus,

$$\frac{\tau_1}{\tau_2} = \frac{r_1 c_1}{r_2 c_2} = k_2 k_3$$

.

#### Problem #8 (Interconnects, 20 points)

The following figure shows a driver  $(K_D)$ , a sink  $(K_S)$ , and evenly-distributed #4n buffers.

Since the buffers are evenly distributed,  $s_1 = s_2 = \cdots = s_{4n+1}$  where  $s_j$  is the distance between  $B_j$  and  $B_{j+1}$  (you can think of  $K_D$  as  $B_0$  and  $K_S$  as  $B_{4n+1}$ ).

However, there is one constraint. A half of the buffers must be BUF\_X1 and the other half must be BUF\_X2. The following shows the characteristics of the buffers:

- BUF\_X1: Output resistance  $(R_0)$ , input capacitance  $(C_0)$ , output capacitance  $(C_m)$ , internal delay  $(d_0)$

- BUF\_X2: Output resistance  $(\frac{R_0}{2})$ , input capacitance  $(2C_0)$ , output capacitance  $(2C_m)$ , internal delay  $(2d_0)$

The driver and the sink are BUF\_X1 buffers.

Problem: Determine the size of each buffer (from  $B_1$  to  $B_{4n}$ ) to minimize the total delay from the driver to the sink.

There are four cases as follows:

- 1) A 1X buffer drives a 1X buffer: Delay  $\tau_{1,1} = R_0(C_m + C_w + C_0) + R_wC_0 + \frac{1}{2}R_wC_w$

- 2) A 1X buffer drives a 2X buffer: Delay  $\tau_{1,2} = R_0(C_m + C_w + 2C_0) + R_w 2C_0 + \frac{1}{2}R_w C_w$

- 3) A 2X buffer drives a 1X buffer: Delay  $\tau_{2,1} = \frac{R_0}{2} (2C_m + C_w + C_0) + R_w C_0 + \frac{1}{2} R_w C_w$

- 4) A 2X buffer drives a 2X buffer: Delay  $\tau_{2,2}=\frac{R_0}{2}(2C_m+C_w+2C_0)+R_w2C_0+\frac{1}{2}R_wC_w$

Whenever a buffer drives a buffer, there is a minimum delay  $R_0C_m + R_wC_0 + \frac{1}{2}R_wC_w$ . In addition, the buffers should anyway drive the wires. Thus, we do not need to think about them. We can only care about the additional terms as follows:

- 1) A 1X buffer drives a 1X buffer: Delay  $\tau_{1,1} = R_0 C_0$

- 2) A 1X buffer drives a 2X buffer: Delay  $\tau_{1,2} = 2R_0C_0$

- 3) A 2X buffer drives a 1X buffer: Delay  $\tau_{2,1} = \frac{R_0 C_0}{2}$

- 4) A 2X buffer drives a 2X buffer: Delay  $\tau_{2,2}=R_0C_0$

Notice that if a 1X buffer drives a 1X buffer, there should be a 2X buffer driving a 2X buffer. The delay of these pairs is  $\tau_{1,1} + \tau_{2,2} = 2R_0C_0$ . Similarly, if a 1X buffer drives a 2X buffer, there should be a 2X buffer driving a 1X buffer. The delay of these pairs is  $\tau_{1,2} + \tau_{2,1} = 2.5R_0C_0$ . Comparing these pairs, the former has a shorter delay. Thus, the answer is to place 2X buffers consecutively. For example,

$$K_D - 1X - 1X - \dots - 1X - 2X - 2X - \dots - 2X - 1X - 1X - \dots - 1X - K_S$$