# EE434 ASIC and Digital Systems

## Midterm Exam 2

Mar. 27, 2019. (4:10pm - 5pm)

Instructor: Dae Hyun Kim (daehyun@eecs.wsu.edu)

#### Name:

## **WSU ID:**

| Problem | Points |  |

|---------|--------|--|

| 1       | 10     |  |

| 2       | 15     |  |

| 3       | 20     |  |

| 4       | 25     |  |

| 5       | 20     |  |

| 6       | 20     |  |

| Total   | 110    |  |

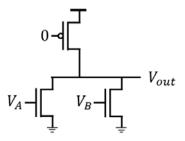

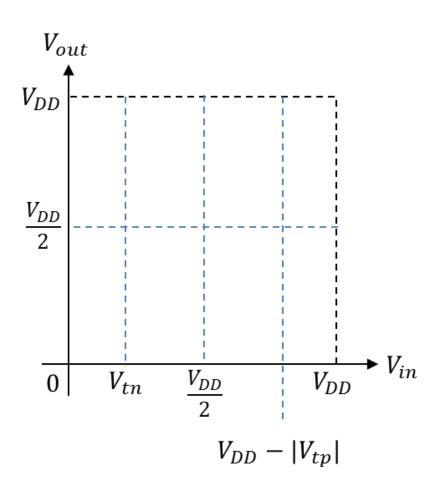

# Problem #1 (DC Analysis, 10 points)

Draw a DC characteristic curve for the following pseudo-NMOS two-input NOR gate. Just a rough sketch will be accepted.

(1) For input AB:  $00 \rightarrow 10$

(2) For input AB:  $00 \rightarrow 11$

## Problem #2 (DC Analysis, 15 points)

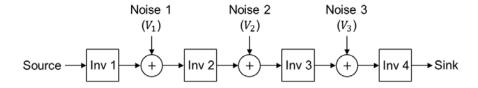

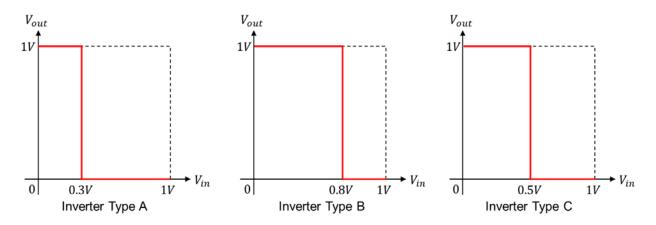

The following figure shows a chain of four inverters with three noise sources. The value at the source node is 0V (for logic 0) or 1V (for logic 1).

The following shows the DC characteristic curves for three types of inverters (Type A, B, C).

(1) (5 points)  $|V_1| \le 0.28V$ ,  $|V_2| \le 0.16V$ ,  $|V_3| \le 0.37V$ . If Inv 1: Type A, Inv 2: Type B, Inv 3: Type C, Inv 4:Type C, will the inverter chain work without logic inversion at the sink node? (Yes / No)

(2) (5 points)  $|V_1| \le 0.15V$ ,  $|V_2| \le 0.45V$ ,  $|V_3| \le 0.25V$ . If Inv 1: Type A, Inv 2: Type B, Inv 3: Type C, Inv 4:Type A, will the inverter chain work without logic inversion at the sink node? (Yes / No)

(3) (5 points)  $|V_1| \le 0.12V$ ,  $|V_2| \le 0.14V$ ,  $|V_3| \le 0.34V$ . If Inv 1: Type C, Inv 2: Type A, Inv 3: Type B, Inv 4:Type A, will the inverter chain work without logic inversion at the sink node? (Yes / No)

# Problem #3 (Delay, 20 points)

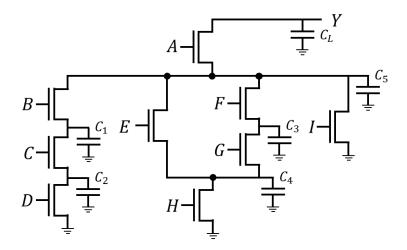

Calculate the Elmore delay of the circuit shown below for the following inputs.  $R_n$  is the resistance of an NFET.  $C_L$  is the load capacitance. All the other capacitances are parasitic capacitances.

- 1) ABCDEFGHI = 111100000

- 2) ABCDEFGHI = 111010010

- 3) ABCDEFGHI = 101101101

- 4) ABCDEFGHI = 111010110

### **Problem #4 (Transistor Sizing, 25 points)**

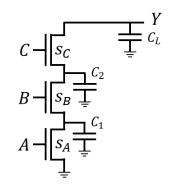

The following figure shows the NFET network of a three-input NAND gate.  $C_L$ : Load capacitance.  $C_1$ ,  $C_2$ : Parasitic capacitance.  $R_n$ : The resistance of a 1X NFET. Assume that  $C_1$ ,  $C_2$ ,  $C_L$  are independent of the widths of the NFETs.  $S_A$ ,  $S_B$ ,  $S_C$ : The width of NFET A, B, C, respectively. "Optimal transistor sizes" means the widths of the transistors that satisfy a given timing constraint and minimize the sum of the widths.

(1) (7 points) Express the Elmore delay of the NAND gate as a function of  $R_n$ ,  $s_A$ ,  $s_B$ ,  $s_C$ ,  $C_1$ ,  $C_2$ ,  $C_L$ .

- (2) (18 points) Answer the following questions.

- (a) If  $C_1$  increases, we should increase the width of transistor A for optimal transistor sizing (True / False).

- (b) If  $C_1$  increases, we should increase the width of transistor B for optimal transistor sizing (True / False).

- (c) If  $C_1$  increases, we should increase the width of transistor C for optimal transistor sizing (True / False).

| (d) If $C_2$ increases, | we should increase | e the width of tra | ansistor $A$ for o | ptimal transistor |

|-------------------------|--------------------|--------------------|--------------------|-------------------|

| sizing (True / False).  |                    |                    |                    |                   |

- (e) If  $C_2$  increases, we should increase the width of transistor B for optimal transistor sizing (True / False).

- (f) If  $C_2$  increases, we should increase the width of transistor C for optimal transistor sizing (True / False).

- (g) If  $C_L$  increases, we should increase the width of transistor A for optimal transistor sizing (True / False).

- (h) If  $C_L$  increases, we should increase the width of transistor B for optimal transistor sizing (True / False).

- (i) If  $C_L$  increases, we should increase the width of transistor C for optimal transistor sizing (True / False).

#### Problem #5 (Interconnect, 20 points)

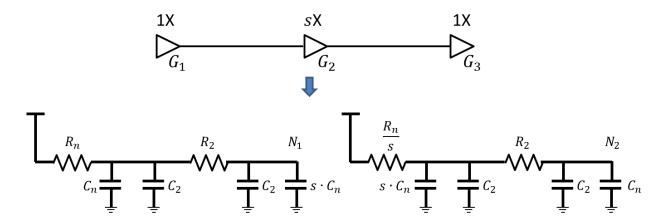

The figure shown above simulates the delay of the signal path from gate  $G_1$  to gate  $G_3$ . For the delay calculation, we use the two RC trees. The left-hand one is for the first half (from  $G_1$  to  $G_2$ ) of the path and the right-hand one is for the second half (from  $G_2$  to  $G_3$ ). The total delay is estimated by the sum of the delays at node  $N_1$  and  $N_2$ .

- $G_1$  and  $G_3$  are 1X cells, so their output resistances, output capacitances, and input capacitances are  $R_n$ ,  $C_n$ , and  $C_n$ , respectively.

- $G_2$  is upsized to sX, so its output resistance, output capacitance, and input capacitance are  $\frac{R_n}{s}$ ,  $sC_n$ , and  $sC_n$ , respectively.

- $R_n$ ,  $C_n$ ,  $C_2$ ,  $R_2$  are constants. s is the only variable in this problem.

- (1) (7 points) Express the total delay as a function of s,  $R_n$ ,  $C_n$ ,  $R_2$ , and  $C_2$ .

(2) (5 points) Express optimal s minimizing the total delay as a function of  $R_n$ ,  $C_n$ ,  $R_2$ , and  $C_2$ .

- (3) (8 points) Answer the following questions.

- (a) If  $R_n$  increases, we should increase s for minimum delay. (True / False)

- (b) If  $C_n$  increases, we should increase s for minimum delay. (True / False)

- (c) If  $R_2$  increases, we should increase s for minimum delay. (True / False)

- (d) If  $C_2$  increases, we should increase s for minimum delay. (True / False)

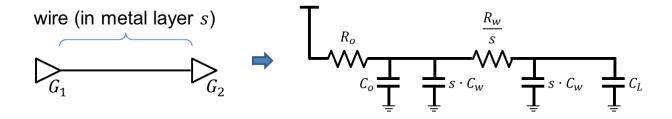

#### **Problem #6 (Interconnect, 20 points)**

The figure shown above simulates the delay of a net routed in metal layer s.

- $R_o$ ,  $C_o$ : Output resistance and capacitance of  $G_1$ , respectively (constants).

- *C<sub>L</sub>*: Load capacitance (constant)

- $R_w$ ,  $C_w$ : Resistance and capacitance of the wire, respectively (constants).

- s: Metal layer (variable)

When we route the net in a layout, we can use any metal layer. If we select an upper layer (e.g., Metal layer 10) for the routing of the net, the resistance of the wire goes down, but the capacitance of the wire goes up. Similarly, if we select a lower layer (e.g., Metal layer 3), the resistance of the wire goes up, but the capacitance of the wire goes down. The RC tree provides a very simple model for the delay estimation.

(1) (5 points) Express the delay from  $G_1$  to  $G_2$  as a function of  $R_o$ ,  $C_o$ ,  $R_w$ ,  $C_w$ ,  $C_L$ , and  $S_1$ .

(2) (5 points) Find s minimizing the delay (express s as a function of  $R_o$ ,  $C_o$ ,  $R_w$ ,  $C_w$ , and  $C_L$ .

- (3) (10 points) Answer the following questions.

- (a) If  $R_w$  increases, we should increase s to minimize the delay. (True / False)

- (b) If  $R_o$  increases, we should increase s to minimize the delay. (True / False)

- (c) If  $C_w$  increases, we should increase s to minimize the delay. (True / False)

- (d) If  $\mathcal{C}_o$  increases, we should increase s to minimize the delay. (True / False)

- (e) If  $C_L$  increases, we should increase s to minimize the delay. (True / False)