### **EE234**

## **Microprocessor Systems**

### Midterm Exam 2

Nov. 15, 2023. (2:10pm – 3pm)

Instructor: Dae Hyun Kim (<u>daehyun@eecs.wsu.edu</u>)

Name:

**WSU ID:**

| Problem | Points |  |

|---------|--------|--|

| 1       | 20     |  |

| 2       | 40     |  |

| 3       | 40     |  |

| Total   | 100    |  |

### Problem #1 (Stack and Subroutines, 20 points)

Correct: +2.5 points. Wrong: -2.5 points. Min: 0.

#### Assume

- The system we are talking about is single-threaded, single-application.

- Function arguments and return values are processed in the stack.

Answer the following questions.

- The maximum size of the stack in a main memory is dependent on the capacity of the main memory. (True / False)

- The maximum size of the stack in a main memory is dependent on the size of the application code being executed. (True / False)

- If a code contains a recursive function call, it might cause a stack overflow error while the recursive function call is being executed. (True / False)

- If a function has many many arguments, calling the function might cause a stack overflow error. (True / False)

- If a function has one argument, calling the function will never cause a stack overflow error. (True / False)

- If a function has no argument, calling the function will never cause a stack overflow error. (True / False)

- If a function has no argument and no return value, calling the function will never cause a stack overflow error. (True / False)

- If a function has no argument, no return value, and no function call in it, calling the function will never cause a stack overflow error. (True / False)

### Problem #2 (Subroutines and Stack, 40 points)

Answer the following questions for the assembly code shown below.

```

com:

main:

PUSH {LR}

PUSH {R0}

LDR R0, [SP, #4]

SUB SP, SP, #8

CMP R0, #1

MOV R0, #5

BGT com 1

MOV R0, #1

STR R0, [SP]

STR R0, [SP, #8]

BL com

POP {LR}

LDR R0, [SP, #4]

BX LR

com 1:

ADD SP, SP, #8

PUSH {R1,R2,R3,R4}

STR R0, [SP, #4]

MOV R1, #0

MOV R2, #1

POP (R0)

SUB R3, R0, #1

end:

com 1 loop:

CMP R2, R3

BGT com 1 loop end

SUB SP, SP, #8

STR R2, [SP]

BL com

LDR R4, [SP, #4]

ADD SP, SP, #8

ADD R1, R1, R4

ADD R2, R2, #1

B com_1_loop

com 1 loop end:

STR R1, [SP, #24]

POP {R1,R2,R3,R4}

POP {LR}

BX LR

```

The main function looks like this in C/C++:

```

int main () {

int s;

..

s = com(5);

...

}

```

### **Problem #3 (Subroutines and Stack, 40 points)**

You should use the following instructions only.

- Instructions

- o ADD, SUB

- o AND, ORR, EOR

- o CMP, BGE/BLT/BGT/BLE/BEQ/BNE

- o B, BL, BX

- o MOV

- o LDR, STR

Write an assembly code for the following C code (the line s=com(a,b) in the main function and the com() function).

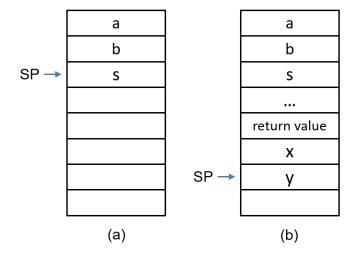

The following shows the memory map for the function call. (a) in the main function. (b) for the function call.

- In the main function, assume that R0-R12 are being used by other variables (right before the function call s=com(a,b)). This means that you should preserve their values if you want to use any of them.

- Use the stack memory for the function arguments and the return value (shown in (b)).

# **Assembly Instructions**

R# is a register. (# =  $0 \sim 12$ )

| Instruction                                    | Meaning                                                                                                                                                            |  |  |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                | Bitwise inversion. (Rd = Bitwise-NOT Ra)                                                                                                                           |  |  |

| MVN Rd, Ra                                     | Before 0 0 0 0 1 1 0 0                                                                                                                                             |  |  |

|                                                | After 1 1 1 1 0 0 1 1                                                                                                                                              |  |  |

|                                                | Bitwise AND. (Rd = Ra AND Rb), (Rd = Ra AND #imm)                                                                                                                  |  |  |

| AND D4 D- Db                                   | Ra   0   0   0   1   1   1   1                                                                                                                                     |  |  |

| AND Rd, Ra, Rb<br>AND Rd, Ra, #imm             | Rb 1 1 1 1 0 1 1 1                                                                                                                                                 |  |  |

| AND Ru, Ra, #IIIIII                            |                                                                                                                                                                    |  |  |

|                                                | Rd 0 0 0 0 0 1 1 1 1                                                                                                                                               |  |  |

| Bitwise OR. (Rd = Ra OR Rb), (Rd = Ra OR #imm) |                                                                                                                                                                    |  |  |

| ORR Rd, Ra, Rb                                 | Ra 0 0 0 0 1 1 0 0                                                                                                                                                 |  |  |

| ORR Rd, Ra, #imm                               | Rb 1 1 0 1 0 0 1 0                                                                                                                                                 |  |  |

|                                                | Rd 1 1 0 1 1 1 0                                                                                                                                                   |  |  |

|                                                | Bitwise exclusive-OR. (Rd = Ra ⊕ Rb), (Rd = Ra ⊕ #imm)                                                                                                             |  |  |

| FOR DAID, DI                                   | Ra 0 1 0 1 0 1 0 1                                                                                                                                                 |  |  |

| EOR Rd, Ra, Rb                                 | Rb 1 1 0 1 0 0 1 0                                                                                                                                                 |  |  |

| EOR Rd, Ra, #imm                               |                                                                                                                                                                    |  |  |

|                                                | Rd 1 0 0 0 0 1 1 1 1                                                                                                                                               |  |  |

|                                                | Logical shift right by (#imm) bits. (Rd = Ra >> #imm)                                                                                                              |  |  |

| MOV Rd, Ra, LSR #imm                           | Ex) #imm = 3                                                                                                                                                       |  |  |

| live v rta, rta, Eert //////////               | Before 1 0 0 0 1 1 0 1                                                                                                                                             |  |  |

|                                                | After 0 0 1 0 0 1 1 0 0 1                                                                                                                                          |  |  |

|                                                | Logical shift left by (#imm) bits. (Rd = Ra << #imm)                                                                                                               |  |  |

| MOV Rd, Ra, LSL #imm                           | Ex) #imm = 3                                                                                                                                                       |  |  |

| , ,                                            | Before   1   0   0   0   1   1   0   1  <br>  After   0   1   1   0   1   0   0   0                                                                                |  |  |

| MOV D I D                                      |                                                                                                                                                                    |  |  |

| MOV Rd, Ra<br>MOV Rd, #imm                     | (Rd = Ra)<br>(Rd = #imm)                                                                                                                                           |  |  |

| ADD Rd, Ra, Rb                                 | (Rd = Ra + Rb)                                                                                                                                                     |  |  |

| ADD Rd, Ra, #imm                               | (Rd = Ra + Rb)<br>(Rd = Ra + #imm)                                                                                                                                 |  |  |

| SUB Rd, Ra, Rb                                 | (Rd = Ra - Rb)                                                                                                                                                     |  |  |

| SUB Rd, Ra, #imm                               | (Rd = Ra - #imm)                                                                                                                                                   |  |  |

|                                                | Set Z = 1 if Rd == #imm. Otherwise, Z = 0. (Z is the Zero field of the CPSR.) Set Z = 1 if Rd == Ra. Otherwise, Z = 0. Notice that N != V is Rd < #imm or Rd < Ra. |  |  |

| CMP Rd, #imm                                   |                                                                                                                                                                    |  |  |

| CMP Rd, Ra                                     |                                                                                                                                                                    |  |  |

| B [addr]                                       | Jump to [addr] unconditionally                                                                                                                                     |  |  |

| BEQ, BNE, BLT, BGT,                            | Branch to [addr] if (BEQ: R1 == R2), (BNE: R1 != R2), (BLT: R1 < R2), (BGT:                                                                                        |  |  |

| BGE, BLE [addr]                                | R1 > R2), (BGE: R1 >= R2), (BLE: R1 <= R2)                                                                                                                         |  |  |

| LDR Rd, [Ra, #imm]                             | Load the data stored at [Ra + #imm] to Rd.                                                                                                                         |  |  |

| STR Rd, [Ra, #imm]                             | Store the data stored in Rd to [Ra + #imm].                                                                                                                        |  |  |