### EE434

# ASIC and Digital Systems

### Final Exam

# May 4, 2021. (1pm – 4pm)

# Instructor: Dae Hyun Kim (<u>daehyun@eecs.wsu.edu</u>)

#### Name:

#### WSU ID:

| Problem | Points |  |

|---------|--------|--|

| 1       | 40     |  |

| 2       | 40     |  |

| 3       | 20     |  |

| 4       | 20     |  |

| 5       | 10     |  |

| 6       | 20     |  |

| 7       | 20     |  |

| 8       | 20     |  |

| Total   | 190    |  |

# Problem #1 (Interconnect Optimization, 40 points)

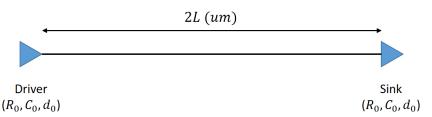

In the figure below, the driver is driving the sink through a long wire. The wire length is 2L (um).

- $R_0, C_0, d_0$ : The output resistance, the input capacitance, and the internal delay of the gates, respectively.

- $r_1, c_1$ : Unit wire resistance and capacitance of metal layer 3

- r<sub>2</sub>, c<sub>2</sub>: Unit wire resistance and capacitance of metal layer 4

Answer the following questions.

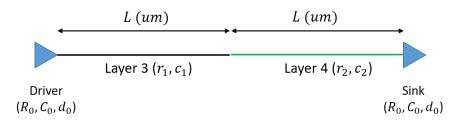

(a) (5 points) The first wire segment is routed on the metal layer 3 and the second wire segment is routed on the metal layer 4 as shown below. Express the total delay  $d_A$  from the output of the driver to the input of the sink as a function of the parameters above.

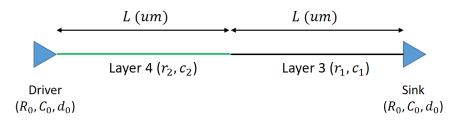

(b) (5 points) The first wire segment is routed on the metal layer 4 and the second wire segment is routed on the metal layer 3 as shown below. Express the total delay  $d_B$  from the output of the driver to the input of the sink as a function of the parameters above.

- (c) (6 points) When are they ( $d_A$  and  $d_B$ ) equal? Show the condition for  $d_A = d_B$ .

- (d) (2 points) If  $r_1 = r_2$  and  $c_1 > c_2$ ,  $d_A > d_B$ . (True / False)

- (e) (2 points) If  $c_1 = c_2$  and  $r_1 > r_2$ ,  $d_A > d_B$ . (True / False)

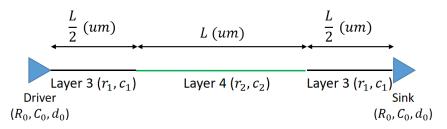

Now, you are supposed to route the driver and the sink using metal layer 3 and 4. However, the total wire length in the metal layer 3 should L (um). Similarly, the total wire length in the metal layer 4 should also be L (um). The following shows an example.

Answer the following questions.

(f) (10 points) If  $r_1 = r_2$  and  $c_1 > c_2$ , how would you route it to minimize the total delay?

(g) (10 points) If  $c_1 = c_2$  and  $r_1 > r_2$ , how would you route it to minimize the total delay?

### Problem #2 (Interconnect Optimization, 40 points)

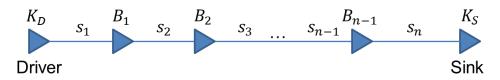

The following figure shows a net optimized by buffer insertion. The driver and the sink are denoted by  $K_D$  and  $K_S$ , respectively, and the inserted buffers are denoted by  $B_i$  ( $1 \le i \le n-1$ ).  $n \ge 2$ , i.e., there is at least one buffer between the driver and the sink.

- Output resistance of  $K_D$ :  $R_D$

- Output resistance of  $B_i$  ( $1 \le i \le n-1$ ):  $R_i$  (e.g.,  $R_1, R_2, ...$ )

- Input capacitance of  $K_S$ :  $C_S$

- Input capacitance of  $B_i$  ( $1 \le i \le n-1$ ):  $C_i$

- Delay of  $B_i$   $(1 \le i \le n-1)$ :  $D_i$

- Length of the *i*-th net  $(1 \le i \le n)$ :  $s_i$  (um)

- $\sum_{i=1}^{n} s_i = L$  (um)

- Unit wire resistance of the *i*-th net  $(1 \le i \le n)$ :  $r_i$  ( $\Omega$ /um)

- Unit wire capacitance of the *i*-th net  $(1 \le i \le n)$ :  $c_i$  (fF/um)

We assume that the net is optimized to minimize the delay from the driver to the sink. Resizing a buffer means upsizing or downsizing the buffer.

Answer the following questions for n = 10 (i.e., we have inserted 9 buffers optimally):

(Correct: +4 points, No answer: 0 point, Wrong: -2 points)

- If  $r_1$  increases and we don't want to resize the buffers, we should increase  $s_1$  to minimize the total delay. (True / False)

- If  $r_1$  increases and we don't want to resize the buffers, we should increase  $s_n$  to minimize the total delay. (True / False)

- If  $c_1$  increases and we don't want to resize the buffers, we should increase  $s_1$  to minimize the total delay. (True / False)

- If  $c_1$  increases and we don't want to resize the buffers, we should increase  $s_n$  to minimize the total delay. (True / False)

- If  $r_1$  increases and we don't want to move the buffers, we should upsize  $B_1$  to minimize the total delay. (True / False)

- If  $r_1$  increases and we don't want to move the buffers, we should upsize  $B_{n-1}$  to minimize the total delay. (True / False)

- If  $c_1$  increases and we don't want to move the buffers, we should upsize  $B_1$  to minimize the total delay. (True / False)

- If  $c_1$  increases and we don't want to move the buffers, we should upsize  $B_{n-1}$  to minimize the total delay. (True / False)

- If  $r_1$  and  $c_1$  increase at the same time and we don't want to resize the buffers, we should increase  $s_1$  to minimize the total delay. (True / False)

- If  $r_1$  and  $c_1$  increase at the same time and we don't want to move the buffers, we should upsize  $B_1$  to minimize the total delay. (True / False)

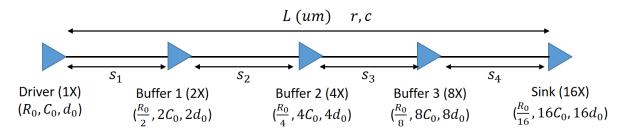

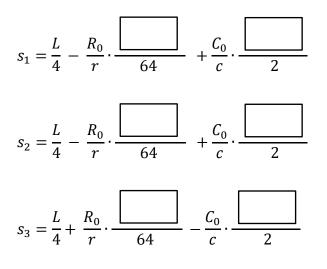

#### Problem #3 (Interconnect Optimization, 20 points)

The following shows a buffer insertion problem. The triplet (R, C, D) of a gate is the (output resistance, input capacitance, internal delay) of the gate.

- L: Net length

- r, c: Unit wire resistance and capacitance

You insert three buffers as shown above (2X, 4X, 8X) to minimize the delay. Find their locations (i.e., find  $s_1, s_2, s_3$ ).

# Problem #4 (Interconnect Optimization, 20 points)

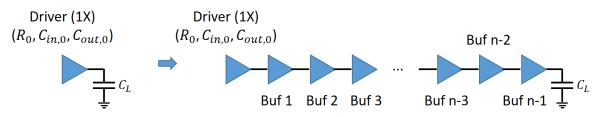

In the following figure (left), the driver is driving a very large load capacitor,  $C_L$ . The triplet (R, C, T) is (output resistance, input capacitance, output capacitance) of the gate. Since it is driving a large load cap, Michael inserts buffers as shown in the figure (right).

The size of Buf *S* is  $k^S \times$ , so the triplet of Buf *S* is  $\left(\frac{R_0}{k^S}, k^S \cdot C_{in,0}, k^S \cdot C_{out,0}\right)$ . In other words, the size of Buf 1 is  $k \times$ , the size of Buf 2 is  $k^2 \times$ , the size of Buf 3 is  $k^3 \times$ , and so on. Michael found an optimal solution, so both *k* and *n* are optimal.

Answer the following questions. Assume n = 10.

(Correct: +5 points, No answer: 0 point, Wrong: -3 points)

- If I upsize Buf 5 from  $k^5 \times \text{to } B \times (B > k^5)$ , I should upsize Buf 3 too for optimal buffer insertion. (True / False)

- If I upsize Buf 5 from  $k^5 \times \text{to } B \times (B > k^5)$ , I should upsize Buf 7 too for optimal buffer insertion. (True / False)

- If C<sub>L</sub> goes down and n is still 10, I should upsize Buf 5 for optimal buffer insertion. (True / False)

- If *C<sub>L</sub>* goes down and I don't want to size the buffers, I should remove some of the buffers (i.e., reduce *n*) for optimal buffer insertion. (True / False)

### Problem #5 (Transmission Gates, 10 points)

Design the following function (draw a transmission-gate-level schematic) using transmission gates only. Available input: *A*, *B*, *C*, *D*, 0 (*GND*), 1 (*VDD*).

$$Y = \overline{A \cdot B \cdot (C \oplus D)}$$

You can use the following symbols for transmission gates.

# TGs ≤8: 10 points, =9: 8 points, =10: 5 points, >10: 2 points

### Problem #6 (Capacitive Coupling & STA, 20 points)

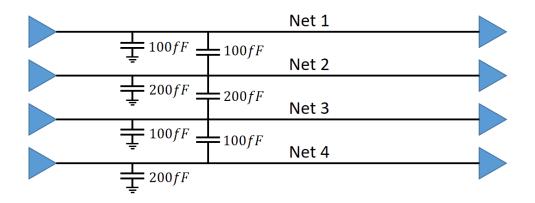

The following figure shows four nets and their ground and coupling capacitances. You can estimate the delay of a net by  $R \cdot C_{eff}$  where *R* is the output resistance of the driver driving the net and  $C_{eff}$  is the effective capacitance of the net.

Assign four given signals  $(S_1, S_2, S_3, S_4)$  to the four nets for signal transmission. You should satisfy the given timing constraints.

- $R: 1k\Omega$  for all the drivers.

- All the drivers have the same arrival time, AT=0ps.

- $S_1$  and  $S_2$  always switch in the same direction.

- $S_3$  and  $S_4$  always switch in the same direction.

- $S_1$  (or  $S_2$ ) and  $S_3$  (or  $S_4$ ) always switch in opposite directions.

| RT (at the sink)              |

|-------------------------------|

| <i>S</i> <sub>1</sub> : 250ps |

| <i>S</i> <sub>2</sub> : 550ps |

| <i>S</i> <sub>3</sub> : 150ps |

| <i>S</i> <sub>4</sub> : 700ps |

(Answer)

(Example)

| <i>S</i> <sub>1</sub> | Net 1 | <i>S</i> <sub>1</sub> — Net 1                |

|-----------------------|-------|----------------------------------------------|

| <i>S</i> <sub>2</sub> | Net 2 | $S_1 = 10000000000000000000000000000000000$  |

| <i>S</i> <sub>3</sub> | Net 3 | $S_3 \xrightarrow{S_4}$ Net 3<br>$S_4$ Net 4 |

| $S_4$                 | Net 4 | <i>S</i> <sub>4</sub> Net 4                  |

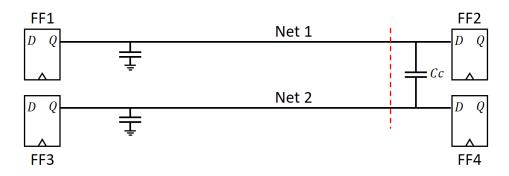

# Problem #7 (Crosstalk & STA, 20 points)

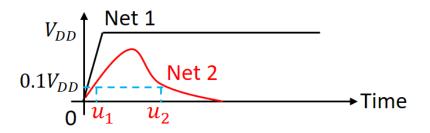

The following figure shows two nets and their coupling (Do not assume that they have the same length.) Notice that the coupling occurs on the right side of the dotted line, which is physically close to FF2 and FF4.

The following figure shows two waveforms when a crosstalk occurs between Net 1 (aggressor) and Net 2 (victim). If the potential of Net 2 is higher than  $0.1V_{DD}$ , signal inversion could happen in Net 2.

- $d_k$ : delay of Net k ( $k = 1 \sim 2$ )

- $s_k$ : setup time of  $FF_k$  ( $k = 1 \sim 4$ )

- $h_k$ : hold time of  $FF_k$  ( $k = 1 \sim 4$ )

- $x_k$ : delay from the clock source to the clock pin of  $FF_k$  ( $k = 1 \sim 4$ )

- $c_k$ : clk-to-Q delay of  $FF_k$  ( $k = 1 \sim 4$ )

- T<sub>CLK</sub>: clock period

(a) Derive a setup time constraint (inequality) related to the crosstalk for Net 2.

(b) Derive a hold time constraint (inequality) related to the crosstalk for Net 2.

# Problem #8 (STA, 20 points)

(a) (5 points) For the setup time analysis, we defined "slack" as "slack = required time – arrival time". In this case, the required time is the time by which the signal should arrive. A positive slack means no timing violation and a negative slack means a timing violation.

Can you define "slack" for the hold time analysis in a similar way? For the hold time analysis, the required time is the time after which the signal should arrive. The goal is to make the slack positive if there is no hold-time violation and negative if there is a hold-time violation.

(b) Answer the following questions for the "hold-time" slack. WNS is the worst negative "hold-time" slack (the smallest slack similar to the definition of WNS for the setup time analysis) and TNS is the total negative "hold-time" slack (the sum of the negative slacks).

(Correct: +3 points, No answer: 0 point, Wrong: -2 points)

- "WNS = TNS" could happen. (True / False)

- "WNS < TNS" could happen. (True / False)

- "WNS > TNS" could happen. (True / False)

- "WNS > 0 and TNS < 0" could happen. (True / False)

- "TNS  $\ll$  0" could happen if many paths have very small delays. (True / False)