# EE434 ASIC and Digital Systems

#### **Final Exam**

May 1, 2024. (1:30pm - 3:30pm)

Instructor: Dae Hyun Kim

Name:

WSU ID:

| Problem | Points |  |

|---------|--------|--|

| 1       | 100    |  |

| 2       | 50     |  |

| 3       | 50     |  |

| 4       | 30     |  |

| 5       | 40     |  |

| 6       | 120    |  |

| Total   | 390    |  |

#### **Problem #1 (Interconnect Optimization, 100 points)**

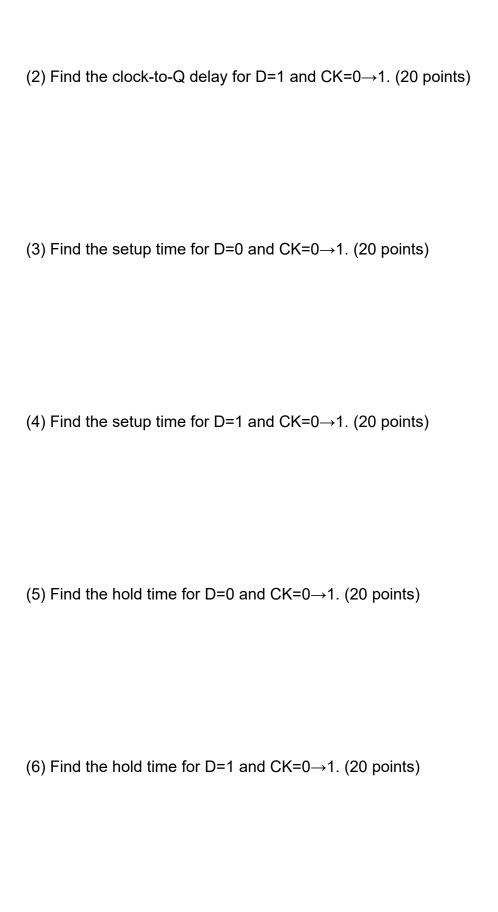

The following figure shows a net optimized by three buffers.

- (A, B, C) of a cell denotes its (input cap., output resistance, internal delay). We ignore all the output capacitances of the cells. r and c are unit wire resistance and capacitance, respectively. L is the length from the Driver to the Sink.

- Given (constants):  $C_0 C_4$ ,  $R_0 R_4$ ,  $d_0 d_4$ , r, c, L

Use the PI model for each wire segment for delay estimation. We want to find optimal x, y, z minimizing the delay from the output of the Driver to the input of the Sink.

(1) Express the delay from the output of the Driver to the input of the Sink <u>after</u> the buffer insertion. (20 points)

(2) Find the optimal locations x, y, z that minimize the delay. (20 points)

- (3) Answer the following questions. Correct: +4 points. Wrong: -4 points. Min: 0 points.

- If *L* increases, then *x* increases. (True / False)

- If *L* increases, then *z* increases. (True / False)

- (4) Answer the following questions. Correct: +4 points. Wrong: -4 points. Min: 0 points.

- If  $R_0$  increases, then z increases. (True / False)

- If  $R_1$  increases, then x increases. (True / False)

- If  $R_1$  increases, then y increases. (True / False)

- If  $R_1$  increases, then z increases. (True / False)

- (5) Answer the following questions. Correct: +4 points. Wrong: -4 points. Min: 0 points.

- If  $R_2$  increases, then x increases. (True / False)

- If R<sub>2</sub> increases, then y increases. (True / False)

- If  $R_2$  increases, then z increases. (True / False)

- (6) Answer the following questions. Correct: +4 points. Wrong: -4 points. Min: 0 points.

- If  $C_2$  increases, then x increases. (True / False)

- If  $C_2$  increases, then y increases. (True / False)

- If C<sub>2</sub> increases, then z increases. (True / False)

- (7) Answer the following questions. Correct: +4 points. Wrong: -4 points. Min: 0 points.

- If  $C_3$  increases, then x increases. (True / False)

- If  $C_3$  increases, then y increases. (True / False)

- If  $C_3$  increases, then z increases. (True / False)

#### **Problem #2 (Interconnect Optimization, 50 points)**

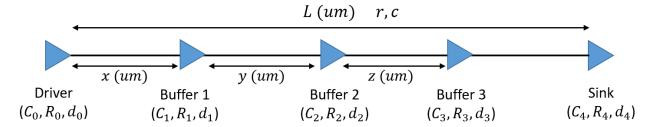

The following figure shows a net optimized by a buffer.

The output resistances of the driver and the buffer are  $R_1$  and  $R_2$ , respectively. The input capacitances of the buffer and the sink are  $C_2$  and  $C_3$ , respectively.  $d_2$  is the internal delay of the buffer.

A new interconnect technology is used for the nets. The nets have no resistance (r=0). However, the wire capacitance is proportional to the square of its length. In other words, the capacitance of a net of length k(um) is  $ck^2$ .

Use the PI model for each wire segment for delay estimation. We want to minimize the delay from the output of the Driver to the input of the Sink.

(1) Express the delay from the output of the Driver to the input of the Sink <u>after</u> the buffer insertion. (10 points)

(2) Find the optimal location x of the buffer that minimizes the delay. (10 points)

- (3) Answer the following questions. Correct: +5 points. Wrong: -5 points. Min: 0 points.

- If *L* increases, then *x* increases. (True / False)

- If  $R_1$  increases, then x increases. (True / False)

- If  $R_2$  increases, then x increases. (True / False)

- If  $C_2$  increases, then x increases. (True / False)

- If  $C_3$  increases, then x increases. (True / False)

- If *c* increases, then *x* increases. (True / False)

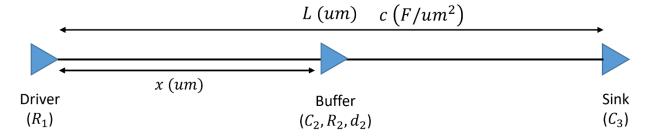

### **Problem #3 (Interconnect Optimization, 50 points)**

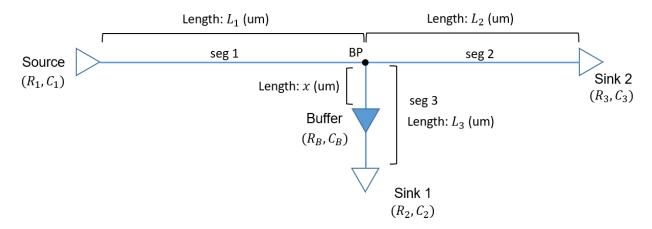

The following figure shows a net having two sinks.

All the nets have the same unit wire resistance (r) and capacitance (c). (A,B) denotes (output resistance, input capacitance). We ignore output capacitance values.

We are going to minimize the delay from the output of the source to the input of the sink 2.

(1) Express the delay from the output of the source to the input of the sink 2. (10 points)

Now, let's insert a buffer into the net. The output resistance and the input capacitance of the buffer is  $(R_B, C_B)$ . Due to some restrictions, we insert the buffer into segment 3 as follows.

(2) Express the delay from the output of the source to the input of the sink 2 after the buffer insertion. (10 points)

- (3) Assume the range of x is  $0 \le x \le L_3$ . We insert the buffer into the location

- right after the branch point (BP) if x = 0.

- right before Sink 1 if  $x = L_3$

- between BP and Sink 1 if  $0 < x < L_3$ .

Find the optimal location of the buffer. (10 points)

- (4) Answer the following questions. Correct: +5 points. Wrong: -5 points. Min: 0 points.

- If  $L_1$  increases, then x increases. (True / False)

- If  $L_2$  increases, then x increases. (True / False)

- If  $L_3$  increases, then x increases. (True / False)

- If  $C_3$  increases, then x increases. (True / False)

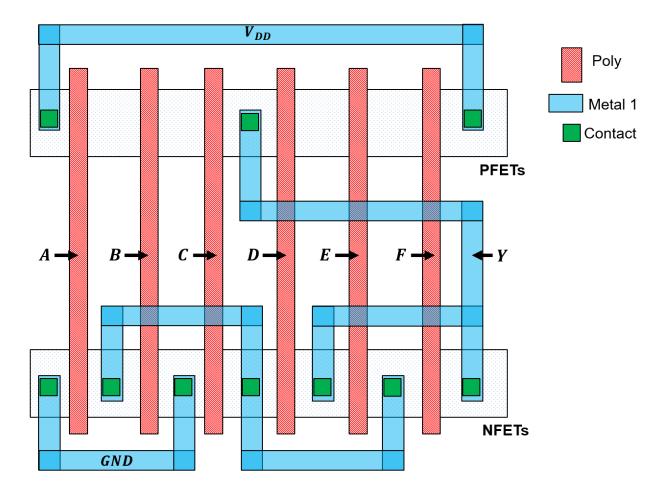

# Problem #4 (Layout, 30 points)

Express the output Y as a Boolean function of the input signals, A, B, C, D, E, F.

(1) Draw a transistor-level schematic for the layout. (20 points)

(2) Express *Y* as a function of the input signals. (10 points)

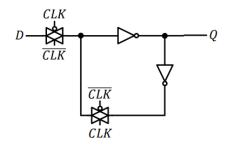

## Problem #5 (Layout, 40 points)

Draw a layout for the following schematic. (It's a D-latch)

• Given input: D, CLK

• Output: Q

You can draw a simplified layout like the one shown in Problem #4. You don't need to show body contacts, n-well, p-well, etc. Use M1 and M2 layers for the metal layers.

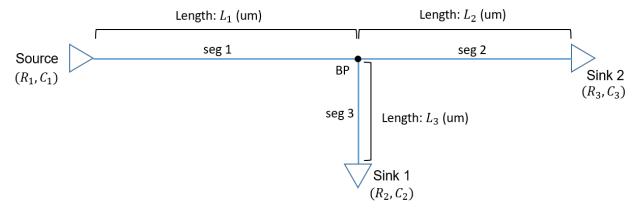

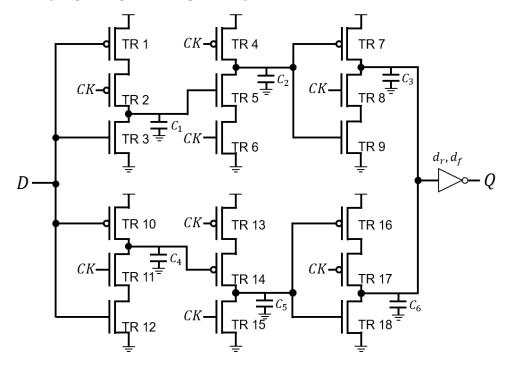

#### Problem #6 (Flip Flops, 120 points)

The schematic above is a dual-edge D-FF design.

- The resistance of the PFET (or NFET) of TR # is  $R_{p,\#}$  (or  $R_{n,\#}$ ). For example, the resistance of the PFET of TR 16 is  $R_{p,16}$ . The resistance of the NFET of TR 18 is  $R_{n,18}$ .

- The rise and fall delays of the inverter are  $d_r$  and  $d_f$ , respectively.

- If an internal node becomes floating, you can assume that it holds its previous value. (i.e., we ignore all the leakage current.)

- If an internal node is not connected to a capacitor, you can ignore its parasitic capacitance.

- (1) Find the clock-to-Q delay for D=0 and CK=0 $\rightarrow$ 1. This means that the DFF captures the value of D=0 when the clock goes high (0 $\rightarrow$ 1) and you are supposed to find the clock-to-Q delay in this case. (20 points)