## EE334 Computer Architecture Homework Assignment 8

Name:

April 9, 2012

There is a benchmark that has the following characteristics.

34% ALU instructions

23% loads (28% of these loads are followed by instructions that need the data being loaded)

15% stores

21% branch instructions (47% of these branches are taken)

7% jumps

This processor's CPI is 1 for the integer instructions (when there are no hazards).

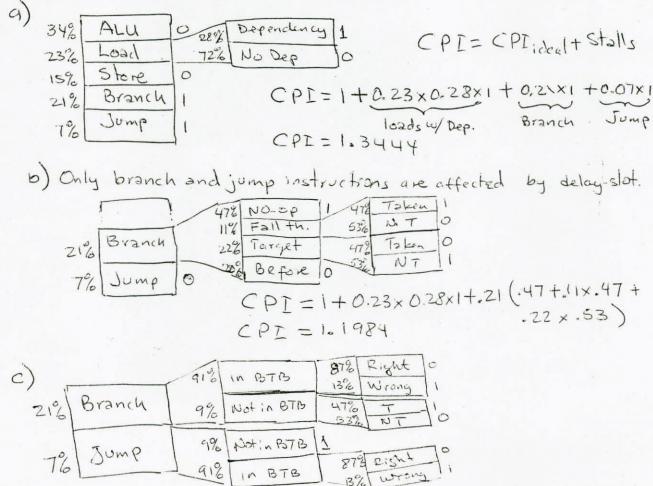

a) Determine the CPI if all branches and jumps have a stall (due to delayed branch with NOP).

b) If the branch-delay slot (after the branches) is scheduled using the three strategies and NO-OP as follows:

| Delay Slot | NO-OP | Fall through | Target | Before |

|------------|-------|--------------|--------|--------|

| %          | 47%   | 11%          | 22%    | 20%    |

The delay slot after the jumps has been scheduled with instructions from the target. Please determine the new CPI.

c) Suppose we add to this processor a branch target buffer (BTB) to predict the branches. When the predictor has an entry (hit) for the branch AND the prediction is right, there is no penalty. When the branch is not found or the prediction of the branch is not right then the penalty is one clock cycle. The prediction hardware for this particular benchmark has the following features: 91% hit rate and 87% correct prediction. Please determine the CPI with branch prediction hardware.